# CS-MAX Compound Semiconductor Mftg Expo July, 2001, Boston MA, Proceedings

## Back-side Processing of GaAs Wafers

Henry Hendriks, Bharat Patel, and Jim Crites

M/A-COM: Tyco Electronics, 100 Chelmsford Street, Lowell, MA 01851, (978) 656-2562, hhendriks@tycoelectronics.com John Moore

General Chemical – Electronic Materials Group, 2340 Bert Drive, Hollister, CA 95023, (831) 630-6202, jmoore@genchemcorp.com

Abstract. Back-side processing of GaAs wafers includes all the manufacturing process steps from just after final front-side electrical test through die separation and packaging. The back-side process flow of a typical GaAs Fab can be separated into two major branches. The first branch is for GaAs die that do not require back-side via holes or metal. The main process steps involved are wafer thinning, dicing, die inspecting, and packaging. The second branch is for die that require back-side metal and in most cases through substrate via holes. This branch involves several additional process steps including wafer / carrier mount, back-side photoresist mask definition, via hole etch, photoresist strip, oxygen plasma clean, seed layer deposition, and electroplating. This presentation will focus on several key back-side process steps that have historically presented problems and discuss some of the recently available options that can be implemented to increase yield and throughput.

#### Introduction

Yield at back-side is crucial to the success of a GaAs Fab as a result of the large investment already made in processing the wafers through front-side. Also, major challenges exist in scaling up from a 4" to 6" diameter wafer platform. Fab equipment vendors over the past few years have taken notice of the growth in demand for GaAs based devices for wireless applications and have started to address some of the tool deficiencies that previously existed at a few of the main back-side process steps. However, the costs of these new tools can be considerable, so Fab process engineers and managers need to carefully review cost of ownership models and future wafer volume requirement estimates in order to justify these capital equipment purchases and installations. The recent decrease in demand for wireless devices illustrates just how challenging these capital equipment purchase decisions can be.

## Back-side Process Flows

Detailed reviews of the GaAs wafer back-side process flows have recently been published. 1-3 For 150 mm diameter wafers that do not require vias and back-metal, an ultra-violet (UV) back-grinding (BG) tape is usually used to protect the wafer front-side. The UV BG tape typically consists of a polyolefin base film, an anti-static layer, an acrylic UV curable adhesive layer, and a polyester backing film, which is peeled off just prior to mounting the tape onto the wafer front-side surface. A cross section for Ultron Systems, Inc UV anti-static tape is shown in Figure 1. Other UV BG tape vendors include Furukawa Electric and Lintec (Adwill series). The thickness of the polyolefin base film can range from 70 to 250 µm and serves as a support for the thinned wafer. The combined thickness of the adhesive and anti-static layers typically ranges from 18 to 40 µm, and the total thickness variation of the tape is usually within ±6 μm. If the wafers have air-bridges, a thick photoresist can be applied to protect the air-bridges during the tape mount and subsequent thinning steps.

For high volume manufacturing, an automatic wafer taper and de-taper are typically used.<sup>4</sup> Automatic taper and de-taper vendors include Takatori, Microcontrol, Teikoku (Okamoto), Lintec (Adwill series), and Nitto Denko. The detaper can be purchased with a UV exposure module option. Upon UV exposure the adhesive layer strength of the tape is reduced to 1-5%. The UV BG de-tape step should be done after the thinned wafers have been mounted on dice tape frames, so that thinned wafers are continuously supported by tape base film from the grind through dice steps. Wafer tape system vendors are developing new automated tools that combine the UV BG de-tape step with the dice tape frame mount step that are targeted for Smart Card applications. Hopefully, these new tools will soon be available for use on 150 mm diameter GaAs wafers. A few GaAs Fabs have demonstrated that 150 mm wafers with UV BG tape are thinned to a target thickness range of 250 to 125 μm with high yield.

An automated single wafer / dual spindle grinder is used to perform most of the wafer thinning followed by a post grind wet etch or polish to remove the grinding damage layer.<sup>2,3</sup> The dual spindle grinder performs a fast, bulk, rough grind followed by a slow, thin, fine grind to achieve high throughput and minimize the thickness of the grinding damage layer. Dual spindle / single wafer grinder vendors include Strasbaugh, Disco, Okamoto, and G&N. Okamoto also offers a post grind wet etch module option for grinding damage removal.

Figure 1: UV tape cross section for Ultron Systems, Inc. P/N 1043

For 100 mm diameter GaAs wafers, a 10-12 µm thick photoresist layer can be used instead of tape to protect the wafer front-side. However, handling and breakage become issues if the wafer is thinned below 150 µm since it is unsupported between the thinning and dice tape fame mount steps.

For wafers that require vias and back-metal, the wafers may be thinned between 100 and 20 µm, which requires that the wafer be mounted on a carrier using a high temperature wax or thermoplastic adhesive.2, 6, 7 Liquid thermoplastic adhesives can be applied using a coat and bake track while dry film adhesives can be applied using a dry film vacuum laminator. Perforated sapphire carriers are currently widely used for 150 mm wafer processing.2,3 However, new automated wafer / carrier mount and de-mount tools may allow for the use of non-perforated carriers.7 offering these tools include BLE, EVGroup, and Karl Suss. BPS Technologies has recently introduced an automated demount tool for use with perforated carriers. Also, glass carrier disc vendors, such as Logitech (Struers, Inc.) and PlanOptiks, have recently introduced doped borosilicate glass carriers with the thermal coefficient of expansion more closely matched to GaAs. These are being tested as a less expensive alternative to sapphire with possible savings of up to several hundred dollars per carrier.2, 8, 9

For post grind wet etch, single wafer and batch tools are available from vendors, such as Semitool and SEZ. Single wafer tools tend to offer a tighter total thickness variation (TTV), while batch tools are much less expensive and have higher throughput.<sup>2, 6, 10</sup> Also, vendors, such as Strasbaugh and Speedfam-IPEC, offer high throughput wafer chemical mechanical polish (CMP) systems that can also be used for back-side GaAs wafer post grind damage removal. With these CMP systems, a TTV of less than 2 μm across a 150 mm diameter wafer can be achieved. However, note the TTV of the carrier plus mounting medium can be as high as 8 μm, which is an issue when the final target thickness of the wafer is 50 μm or less.<sup>2, 8, 9</sup>

High density plasma etch tools based on ICP and dual frequency enable single 150 mm diameter wafer via etch processing with high throughput, even for individual source vias (ISVs), which fit within 30 µm long front-side source pads of power FET devices. 11-13 This allows better heat conduction away from the hot active regions of the device. 14.

15 Vendors offering high density plasma etch tools for via etching include Oxford, STS, Tegal, Trikon, and Unaxis. 11 For high aspect ratio ISVs, bias, long throw, or collimated sputter deposition may be required to ensure conformal seed layer deposition through the vias. 16 Some 150 mm Fabs with ISV capability have gone to a cluster platform with individually configured chambers. The cluster platforms are available from Trikon, Unaxis, and Veeco. For Fabs with less stringent via aspect ratio requirements, an automated batch sputter system from vendors such as Astex, TEL, and Unaxis, can be used for seed layer deposition. 1, 3

Wafer electroplating systems with pulse capability and carefully engineered solution circulation are being used to deposit a conformal thick gold layer (3 to 8 µm) onto the back-side surface and through the ISVs. Vendors marketing wafer plating systems to GaAs Fabs include EEJA, Reynolds Tech, Semitool, and Technic. For wafers to be thinned to 50 μm or less, a thicker back-side gold layer can improve the mechanical strength of the thinned wafer at the expense of slower throughput at the plating step. If the die are to be attached to packages or carriers for module assembly using a high thermal conductive epoxy, then a solder-stop layer inside the vias is unnecessary. If the die are to be attached using Au-Sn eutectic solder pre-forms, then a solder-stop metal, such as Ti, TiW, Ni, or Cr, that readily oxidizes needs to be deposited inside the vias to prevent solder from "blowing out" the frontside metal pads.1,3 The solder-stop layer can be deposited by either sputter deposition or electroplating. photolithography / wet etch process is typically used to completely clear the solder-stop from the back-side metal plane in order to minimize voiding at this interface during the die attach step. For large via openings at the back-side surface, the thick, positive, liquid photoresist flows into and fills the via during the dispense step. This enables a flood exposure and develop process to be used after back-side dicing streets have been defined saving one contact mask step.<sup>1, 3</sup> During the photoresist bake step, it is possible for some solder-stop metal to diffuse slightly into the thick gold layer along grain boundaries. This small concentration of diffused metal can later oxidize and create voiding problems at the solder die attach step. A quick fix to this problem is to implement a short gold wet etch (either potassium iodide or cyanide based) to lift off the solder stop metal imbedded in the grain boundaries. Finally, the photoresist mask is wet stripped, and then the thinned wafers can be de-mounted from the carriers.<sup>1-3, 6</sup>

Dicing of thinned wafers less than or equal to 100 µm thick may require the use of UV dice tape, especially if the wafers are to be sawn. The structure of UV dice tape is very similar to that of UV BG tape as shown in Figure 1. Vendors recommend that the UV dice tape be exposed within 24 hours after the wafer is mounted on a tape frame in order to ensure that residue from the adhesive binder is not left on the die after pick & place. The is not followed, then residue can potentially lead to problems if a Au-Sn cutectic solder die attach step is used. Upon UV exposure the adhesive strength of the tape is decreased between one and two orders of magnitude. This enables thin, fragile die to be pick & placed from the dice tape. 19, 20

#### Au-Sn Eutectic Solder Die Attach

Most GaAs device die with back-metal are attached to packages or module carriers using conductive thermoset epoxy. However, for high power devices, a Au-Sn eutectic solder with a melt temperature of 280°C may be needed to satisfy the thermal conduction requirements between the active region of the device and the heat sink. The two main tool platforms for Au-Sn die attach are a pick & place, hot forming gas die bonder and reflow oven.20-24 With the recent advances made in robotics, vendors, such as Palomar Technologies and MRSI Group, now offer fully automated platforms. 20, 24 For high power devices that need to be die attached using Au-Sn eutectic solder, a smaller die size is desired to achieve a more robust die attach process.20 A voidfree die attach may be required to ensure adequate thermal conduction of heat away from the power amplifier active regions. For the pick & place die bonders, larger size die typically require a higher forming gas flow in order to promote an increased heat transfer rate and reduce voiding between the solder pre-form and die back-metal surface. Also, a programmed scrub breaks down the tin-oxide on the pre-form prior to forming gas flow.

C-SAM (C-mode Scanning Acoustic Microscopy) can be used as a periodic screen test to check for excessive voiding between the die and carrier after die attach. 21-23 It is also useful in optimizing a die attach process. Since the package or module needs to be submerged in DI water, the test can be destructive if it is non-hermetically sealed. C-SAMs of three Au-Sn eutectic solder pre-form die attachments done with a pick & place, gas die bonder are shown in Figure 2. The first die attach was essentially voidfree since tiny voids occurred only at the vias, which are lined with solder-stop metal. The second die attach had a few large voids as a result of residual solder-stop metal on the die backmetal surface. This was confirmed by Auger Microanalysis. The third die attach has a large void due to partial wetting of the pre-form. This was traced to a forming gas nozzle

misalignment, contributing to a partial pre-form to reach the eutectic melt temperature.

a. Good die attach

Residual solder-stop

c. Gas nozzle mis-aligned

Figure 2: C-SAMs of void-free and void problem Au-Sn solder pre-form die attach. Voids are white.

Depositing Au-Sn directly onto the back-side of the wafer is being explored as an alternative to the use of Au-Sn eutectic pre-forms, stamped to accommodate specific die sizes. The Au and Sn can either be deposited sequentially 25, or jointly<sup>27</sup> to try and achieve the eutectic composition needed for die attach. Also, a Au "sealcoat" layer can be deposited to prevent the Sn from oxidizing before or during the die attach.25, 26 This should lessen the demands on the scrub and hot forming gas flow steps to reduce surface oxides. The eutectic Au-Sn pre-form thickness is typically in the range of 25 µm, necessitating the use of a solder-stop layer inside the vias. The deposited Au-Sn layer or total composite layer thickness can be tailored to obviate the need of a solderstop layer. With the recent advances made in wafer electroplating equipment, depositing Au-Sn directly onto the wafer back-side may shortly move from the R&D phase into manufacturing.

## Temporary Wafer / Carrier Mounting

Wafers that require back-side vias and metal need to be mounted on a carrier using a mounting adhesive. These adhesives are available in a variety of forms such as sticks, films, and liquids. 1-3, 6-9, 28 Although each adhesive may offer its own benefit in mounting, the most robust system will be that one which maintains its integrity during each back-side step. At least one vendor, General Chemical Corporation (GCC), is promoting the benefits and cost savings to Fabs through the use of an entire materials support program for back-side processing. 29

Most adhesives used in wafer mounting exhibit thermoplastic character. Heat is commonly used to achieve uniform metrology and adhesion. Adhesives may be heated to aid flow, topology penetration, and wetting. Taken together, these will produce a smoother surface in preparation for mounting. <sup>28</sup>

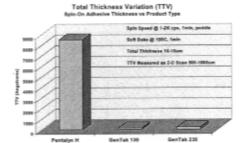

During wafer to carrier mounting, maintaining substrate planarity and uniformity is believed to be a key parameter in successful thinning. Good surface planarity, usually measured as a low TTV, is believed to reduce both internal stress and wafer bow during grinding. So, 30-32 Liquid spin-on forms of adhesives offer easy control of TTV. However, variations in TTV for certain spin-on adhesives exist. Pentalyn<sup>TM</sup>H 33, a customer's prepared product, and GenTak<sup>TM 34</sup>, a ready-to-use dual polymer system, are shown in Figure 3 to have a TTV of nearly 10 and 0.03%, respectively, for a 10um target thickness.

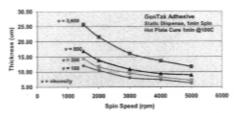

GenTak<sup>TM</sup> may be available in a variety of viscosities offering flexibility in the application to different substrates. Different viscosities allow a variety of ways to achieve planarization of different topographies and to coat-up a range of thicknesses as shown in Figure 4.

Figure 3: TTV of cured spin-on adhesives.

An ideal spin-on adhesive should have wafer edge bead and cured residue on coating equipment easily removed with commodity solvents, such as PGMEA or acetone, as well as be compatible with the existing resist waste stream. So Certain spin-on adhesives, such as GenTak<sup>TM</sup>, offer full compatibility with the use of common positive resists.

#### Resin Application via Spin Coater Thickness vs Spin Speed

Figure 4: GenTak<sup>TM</sup> liquid adhesive application spin curves.

Once the adhesive is applied and cured, mounting proceeds through a thermo-mechanical process. Typically, temperature, pressure, and time are controlled. However, these parameters and the extent to which they are controlled will depend upon the adhesive, coating method, mounting tool, and whether or not perforations exist in the carrier. In all cases bonding and flow temperatures in excess of subsequent back-side processing temperatures are warranted in order to reduce out-gassing and prevent undesired adhesive flow.

## Substrate / Adhesive-Safe Via Cleaning

Dry etching of vias using ICP, high density dual frequency, or RIE requires sidewall passivation in order to achieve an anisotropic profile. During the plasma process, small amounts of organic residue from the eroded photoresist mask is redeposited upon the via sidewalls. This sidewall residue is usually very thin on the order of angstroms. The sidewall residue composition is commonly an amorphous mix of plasma substrate ions, resist by-products, and plasma reactants, which form unknown organometallics.<sup>36</sup> This passivation layer must be removed prior to back-side metal deposition.

Via cleaning is commonly done through chemical stripping with solutions having high levels of amines.<sup>37</sup> These chemistries are time intensive and require a balance between cleaning performance and unwanted substrate etching or adhesive removal. An alternative approach exists in using adhesive and substrate safe materials with robust agitation utilizing ultrasonics. The combination of specialty chemistries, such as GCC's GenSolve<sup>TM</sup> 600 series,<sup>38</sup> and using high frequency ultrasonics at low generator power are showing

### Summary

The two branches of back-side wafer process flows for a typical GaAs Fab were presented. New equipment and methods that have recently become available to handle some of the historically troublesome steps were discussed. Emphasis was placed on the Au-Sn eutectic die attach and the temporary wafer / carrier mounting steps. Through the use of robust applications and high performance materials, backside processing of GaAs wafers can be optimized to reach high volume throughput and yield requirements.

#### References

- <sup>1</sup>H. Hendriks, G. D'urso, and C. Varmazis, "How to Process the Backside of GaAs Wafers", Semicond. Internat. 23-14, 87 (2000).

- <sup>2</sup>L. S. Klingbeil, K. L. Kirschenbaum, C. G. Rampley, and D. Young, "150mm Through Substrate Interconnect Conversion One Year Later", GaAs MANTECH Conf. 2001, p. 41-44

- <sup>3</sup>H. Hendriks, J. Crites, G. D'urso, R. Fox, T. Lepkowski, and B. Patel, "Challenges in Rapidly Scaling up Back-side Processing of GaAs Wafers", GaAs MANTECH Conf. 2001, p. 181-184.

- <sup>4</sup>J. Muller, P. Stamka, W. Kroninger, E. Gaulhofer, and H. Oyrer, "Smart Card Assembly Requires Advanced Pre-Assembly Methods", Semicond. Internat. 23-7, 191 (2000).

- <sup>5</sup>For example: Nitto Denko America, Inc., Model MHR-8500 wafer dice tape mounter, Fremont, CA.

- <sup>6</sup>K. M. Adams and L. S. Klingbeil, "Breaking the 1000 Wafers/ Week Barrier Through Substrate Via Process", GaAs MANTECH Conf. 2000, p. 75-78.

- <sup>7</sup>W. Bosch, "Filtronic exploits the benefit of pHEMTs", Compound Semicond. 7-4, 87 (2001).

- <sup>8</sup>T. Glisner, T. Luxbacher, P. Linder, C. Schaefer, R. Michaels, J. Palenksy, V. Dragori, and M. Reiche, "Reversible and Permanent Wafer Bonding for GaAs Processing", GaAs MANTECH Conf. 2001, p. 192-195.

- <sup>5</sup>K. W. Torrance, J. McAnemy, and M. Robertson, "Wax Mounting, Backlapping, and Chemo-Mechanical Polishing of 150mm (6 Inch) GaAs Wafers", GaAs MANTECH Conf. 1999, p. 183-185.

- <sup>10</sup>M. E. Grupen-Shermansky and C. L. Pilote, "A Novel Wafer Thinning Process for GaAs or Si", GaAs MANTECH Conf. 1994, p. 167-170.

- <sup>11</sup>R. Szweda, "Production etch processing for GaAs", III-Vs Review 13-5, 48 (2000).

- <sup>12</sup>E. W. Berg and S.W. Pang, "Low-Pressure Etching of Nanostructures and Via Holes Using an Inductively Coupled Plasma System", J. Electrochem. Soc. 146, 775 (1999).

- <sup>15</sup>P. S. Nam, L. M. Ferreria, T. Y. Lee, and K. N. Tu, "Study of grass formation in GaAs backside via etching using inductively coupled plasma system", *J. Vac. Sci. Technol. B* 18, 2780 (2000).

- <sup>14</sup>K. J. Nordheden, D. W. Ferguson, and P. M. Smith, "Reactive ion etching of via holes for GaAs high electron mobility transistors and monolithic microwave integrated circuits using Cl<sub>2</sub>/BCl<sub>3</sub>/Ar gas mixtures", J. Vac. Sci. Technol. B 11, 1879, (1993).

- <sup>15</sup>K. J. Nordheden, X. D. Hua, Y. S. Lee, L. M. Yang, D. C. Streit, and H. C. Yen. "Smooth and anisotropic reactive ion etching of GaAs slot via holes for monolithic microwave integrated circuits using Cl<sub>2</sub>/BCl<sub>3</sub>/Ar plasmas", J. Vac. Sci. Technol. B 17, 138, (1999).

- <sup>16</sup>R. A. Powell and S. M. Rossnagel, <u>Thin Films PVD for Microelectronics: Sputter Deposition Applied to Semiconductor Manufacturing</u>, Academic Press, Boston, MA, 1999.

<sup>17</sup>D. Moore, "Sticky Issues with Semiconductor Processing Tape",

- <sup>17</sup>D. Moore, "Sticky Issues with Semiconductor Processing Tape". Semicond. Internat. 19-5, 139 (1996).

- <sup>18</sup>Furukawa Electric Co., "Handling Manual for UV-Curable Tape", www.wadsworth-nacific.com.

- www.wadsworth-pacific.com.

<sup>19</sup>D. L. Monthei, <u>Package Electrical Modeling</u>, <u>Thermal Modeling</u>, and <u>Processing for GaAs Wireless Applications</u>, Kluwer Academic Pubishers, Norwell, MA, 1999.

- <sup>20</sup>M. Chalsen and D. Crowley, "Build GaAs Modules in High Volumes", *Microwaves & RF* April 1999, p. 99-107.

- <sup>21</sup>G. S. Matijasevic and C. C. Lee, "Void-Free Au-Sn Eutectic Bonding of GaAs Dice and its Characterization Using Scanning Acoustic Microscopoy", *J. Electron. Mat.* 18, 327 (1989).

- <sup>22</sup>C. C. Lee and G. S. Matijasevic, "Highly Reliable Die Attachment on Polished GaAs Surfaces Using Gold-Tin Eutectic Alloy", *IEEE Trans. Comp.*, Hybrids, and Manuf. Technol. 12, 406 (1989).

- <sup>23</sup>M. Nishiguchi, N. Goto, and H. Nishizawa, "Highly Reliable Au-Sn Eutectic Bonding with Background GaAs LSI Chips", *IEEE Trans.* Comp., Hybrids, and Manuf. Technol. 14, 523 (1991).

- <sup>24</sup>Z. Bok, "Automated eutectic die attach: Ideal for telecom and datacom", Advanced Packaging April 2000, p. 35-39.

- <sup>25</sup>C. C. Lee, C. Y. Wang, and G. S. Matijasevic, "A New Bonding Technology Using Gold and Tin Multilayer Composite Structures", *IEEE Trans. Comp., Hybrids, and Manuf. Technol.* 14, 407 (1991).

<sup>26</sup>C. C. Lee and C. Y. Wang, "A low temperature bonding process

- using deposited gold-tin composites", *Thin Film Solids* **208**, 202 (1992).

- <sup>27</sup>B. Djurfors and D. G. Ivey, "Film growth characterization of pulse electrodeposited Au/Sn thin films", GaAs MANTECH Conf. 2001, p. 181-184.

- <sup>28</sup>J.Moore, "Materials and Conditions Used to Optimize Thinning, Processing, and Dismounting GaAs Wafers", SEMICON-WEST 2001 SEMI Technical Symposium (STS): Innovations in Semiconductor Manufacturing, p. 339-348.

- <sup>29</sup>General Chemical Corporation, "GenSolutia<sup>TM</sup> Products for Compound Semiconductor Wafer Backside Processing", file: backsideprofile.pdf, July 2001, www.genchemcorp.com.

- <sup>30</sup>C. Orlando, T. Goodrich, and E. Gosselin, "Backside Mounting Procedures for Semiconductor Wafer Processing", GaAs MANTECH Conf 2001, pp. 189-191.

- <sup>31</sup>I. Blech and D. Dang, "Silicon Wafer Deformation After Backside Grinding, Solid State Technology, August 1994, pp. 74-76.

- <sup>32</sup>C. McHatton and C. Gumbert, "Eliminating Backgrind Defects With Wet Chemical Etching, Solid State Technology, November 1998, pp. 85-90.

- <sup>33</sup>Pentalyn<sup>TM</sup> H is a tradename of Hercules Corporation.

- $^{34}\mbox{GenTak}^{TM}$  is a tradename of General Chemical Corporation.

- <sup>35</sup>R. Puligadda, R. Huang, C. Cox, J. Lamb III, M. Arjona, and J. Claypool, "New Fast Bottom Antireflective Coatings for 248nm Lithography", SPIE, 2001.

- <sup>36</sup>G. Franz, W. Hosler, and R. Treichler, "Sidewall Passivation of GaAs in BCl<sub>3</sub>-Containing Atmospheres", J. Vac. Sci. Technol., B 19(2), Mar/April 2001, pp. 415-419.

- <sup>37</sup>I. Ward, U.S. Patents 5,419,779 & 5,496,491, Ashland Inc.

- <sup>38</sup>GenSolve<sup>TM</sup> is a tradename of General Chemical Corporation.

- <sup>39</sup>Ueberreiter, K., In <u>Diffusion in Polymer</u>; Crank, J.; Park, G. S., Ed.; Academic Press: New York, 1968; Ch. 7.

- <sup>40</sup>Surfactant Science and Technology, Myers, D., VCH Publishers, Inc., New York, 1988; Ch. 1.

- <sup>41</sup>T. Piazza and W. Puskas, "The Ideal Ultrasonic Parameters for Delicate Parts Cleaning", CAE ULTRASONICS, Internal Brochure.

- <sup>42</sup>J. Moore, "Metal Lift-Off Processing Through Resist Stripping Practices", Internal Laboratory Reports, General Chemical Corporation, 2000-01.

- <sup>43</sup>M. Hodnett, B. Zeqiri, N. Lee, and P. Gelat, "Report on the Feasibility of Establishing a Reference Cavitating Medium", NPL Report CMAM 58, National Physical Laboratory, March 2001.

- <sup>44</sup>M. Hodnett, B. Zeqiri, and T. Leighton, "A Strategy for the Development and Standardization of Measurement Methods for High Power/Cavitating Ultrasonic Fields: Final Project Report", NPL Report CIRA (EXT)016, National Physical Laboratory, January 1997.

<sup>45</sup>S. Bushong, and B. Archer, <u>Diagnostic Ultrasound</u>, Mosby-Year Book, Inc., Missouri, 1991; Ch. 1.

- <sup>46</sup>P. Gelat, M. Hodnett, and B. Zeqiri, "Establishing a Reference Ultrasonic Cleaning Vessel", NPL Report CMAM 55, National Physical Laboratory, September 2000.