# DaeBond 3D<sup>TM</sup> A High Throughput Thin Wafer Support Technology for 3DIC

Jared Pettit, Alex Brewer, David Young, Alman Law, and John Moore Daetec, LLC

March 2014

#### New Wafer Process for 3DIC

#### Technology Abstract

- DaeBond 3D<sup>TM</sup> is a disruptive technology

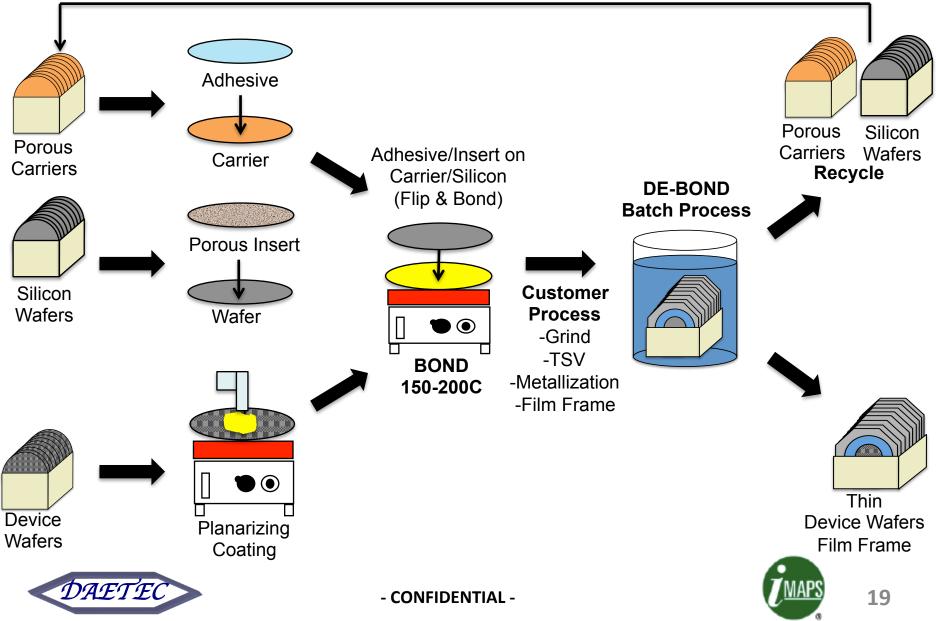

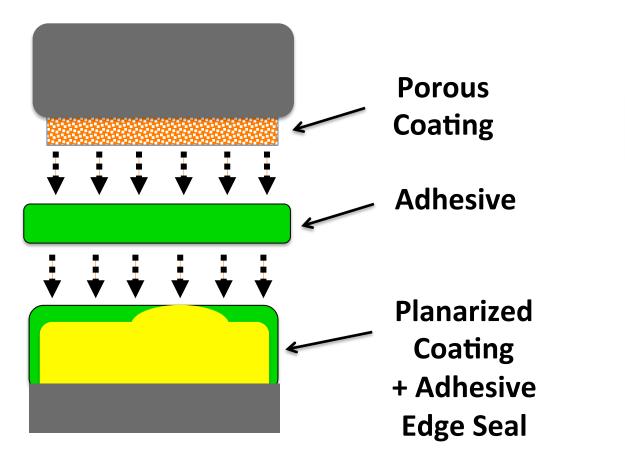

- Device wafers are planarized with an inert coating, bonded to a porous coated carrier, and processed.

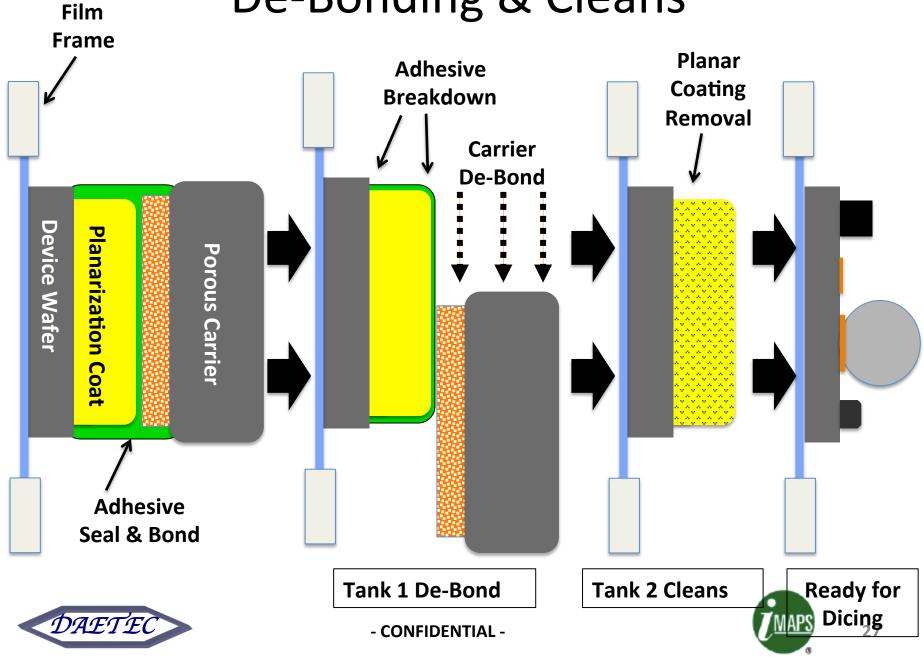

- De-bonding occurs by capillary-driven penetration through the porous layer.

- Carrier release is <15min while the device wafer is supported onto a taped film frame.

- The batch driven process is conducted in a simple wet bench where cost and throughput is defined by cassette size

# Agenda

- 1. Background

- 2. 3DIC Technology Status

- 3. DaeBond 3D<sup>TM</sup>

- 4. Summary

# 1. Background

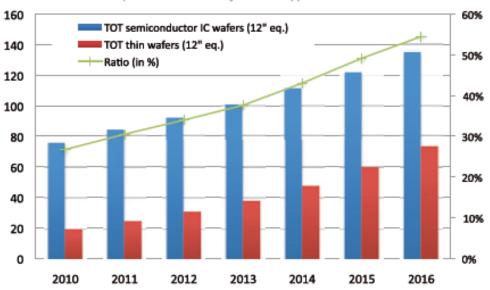

#### Trending to Thin Substrates

- 25% thinned

- Soon to be 50%

#### Ratio of thinned wafers vs. total number of shipped wafers

(volume in millions of 300mm eq.)

Courtesy: Yole Development

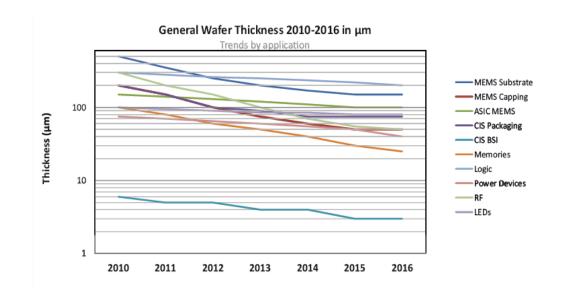

# Thinning below 100um

- Most are <100um</li>

- Current target<50um</li>

- ~5yrs <30um

Courtesy: Yole Development

#### Daetec's Model

- Historically, Daetec is an open innovation technology development firm

- Completed >25 tech transfers, ~6mos ea.

- Focus on thin substrate handling, cleaning

- Markets include semiconductor & display

- This year, product sales have begun in our division: www.waterwashtech.com

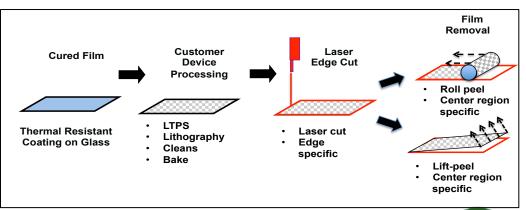

## Daetec's Enabling Technologies Processing Thin Display Substrates

#### **Thin Glass**

#### **OLED Films**

## Daetec's Enabling Technologies Processing Semiconductor Substrates

# **Process Development**

- CONFIDENTIAL -

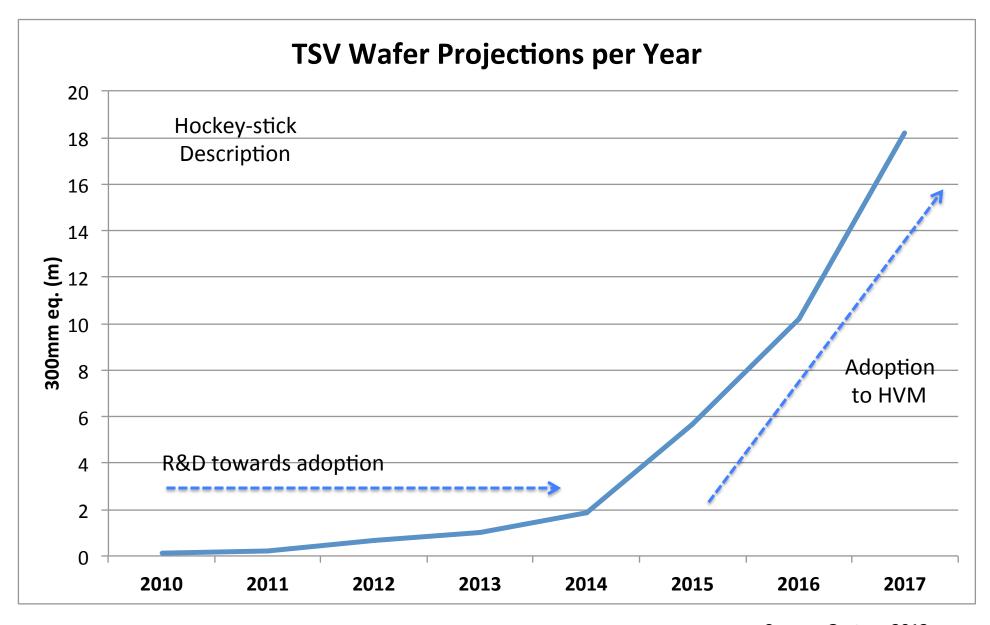

# 2. 3DIC Technology Status

- Semicon-West 2013 panel of experts:

- 3DIC is one of the top industry challenges

- Devices manufactured at <30nm node require flipchip, bump, and creative connectivity

- Tool costs are high and of low throughput

- TSV etch, plating, bond/de-bonders, \$1.5-8m each

- Target 20wph

- 450mm scaling is unknown

# 3DIC Enabled by Temporary Thin Wafer Support

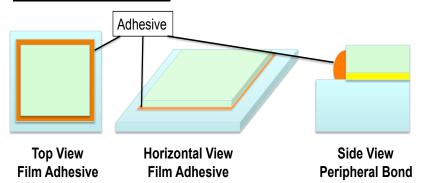

- Adhesive: Mount device wafer to carrier

- Carrier: Silicon or glass, sapphire

- <u>Temporary</u>: Meet mechanical and chem. resistance, seal front side, remove

- <u>Backside processing</u>: Insert connections (lithography, etch, metallize)

- Debond: simple, low cost, substrate safe

- Cleaning: complete, no residue

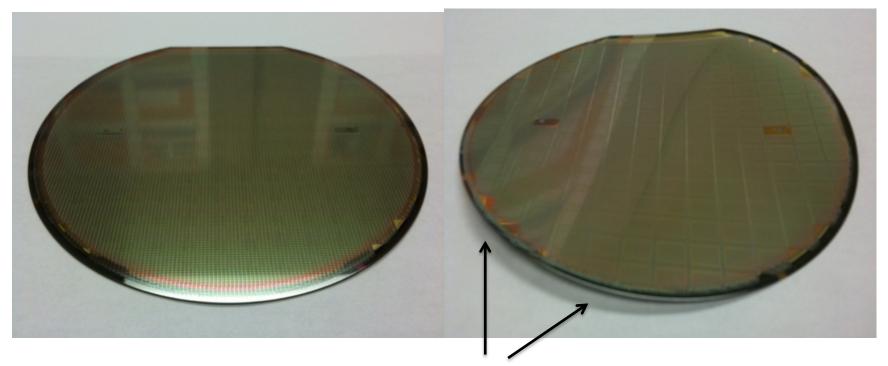

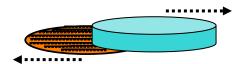

# Thin Wafers Require Support

Full thickness ~ 700um

Thinned ~ 100um

Stress introduction causes wafer bow

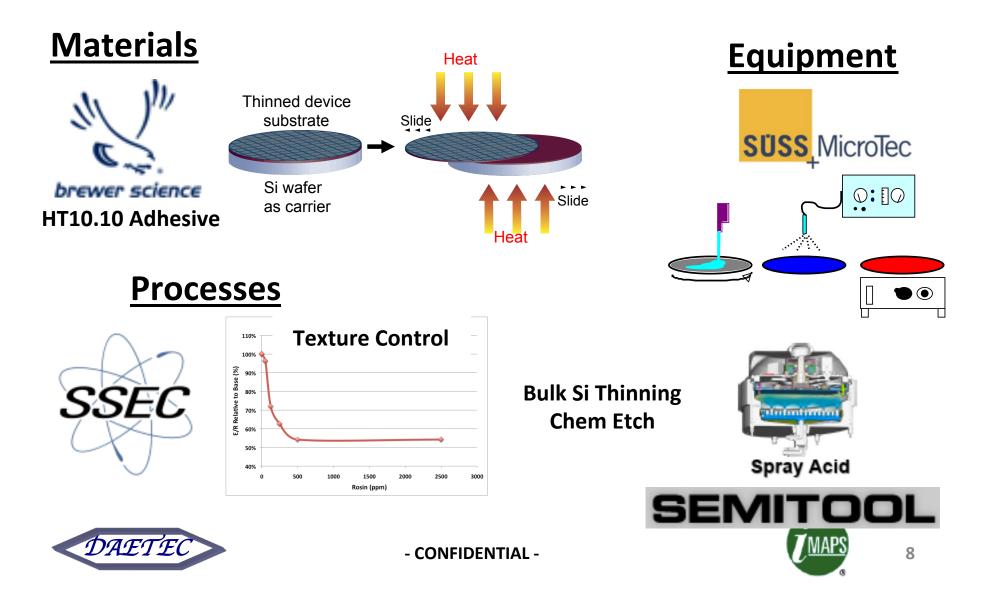

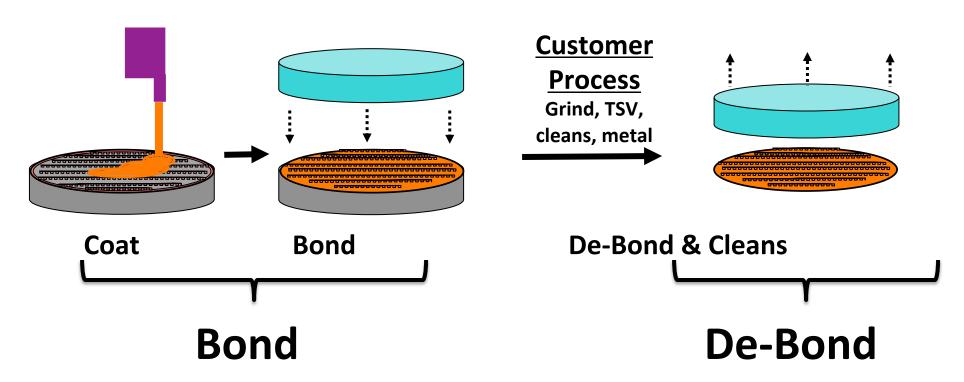

# **Temporary Bonding Process**

Two ACTIVE steps

"Bonding" is similar between all

Differences occur during "De-bond".

# **Existing Technologies**

| Supplier        | Product                                  | Chemistry | Thermo-<br>reaction | De-bond                                                   | Process Type                   |

|-----------------|------------------------------------------|-----------|---------------------|-----------------------------------------------------------|--------------------------------|

| BSI             | WaferBond 1M                             | Rubber    | Plastic             | Chem. diffusion w/perf. carriers, thermal slide, ZoneBond | Single & batch (perf. carrier) |

| 3M              | LTHC <sup>TM</sup> & LC-series           | Acrylic   | Set                 | Laser assisted debond + peel                              | Single                         |

| DuPont          | HD <sup>IM</sup> 3000-<br>series         | Polyimide | Plastic             | Chem. diffusion w/perf. carriers, laser ablation          | Single                         |

| TMAT            | Release layer + adhesive                 | Silicone  | Set                 | Pull-apart                                                | Single                         |

| Dow-<br>Corning | WL-series<br>adhesive +<br>release layer | Silicone  | Set                 | Pull-apart                                                | Single                         |

| TOK             | Zero Newton                              | Urethane  | Plastic             | Chem. diffusion w/perf. carriers                          | Batch (perf. carrier)          |

| DOW             | Cyclotene                                | BCB       | Set                 | Chem. diffusion w/perf. carriers                          | Batch (perf. carrier)          |

# Roadmap to Dicing

Film **Attachment Carrier Demount**

**Wafer Cleans Safe for Tape**  **Dicing**

cleans compatible to tape or vice-versa

#### Barriers to 3DIC

- Single wafer process, perforated carrier

- Low yield physical stress to device wafer

- Low throughput have 8-12 wph, want 20

- Unsupported thin substrate

- Cleans not compatible with tape film frame

- High tool cost

- Carrier not recyclable

- Not scalable

# 3. DaeBond 3D<sup>TM</sup>

| Benefits               | Explanation                                                      |  |

|------------------------|------------------------------------------------------------------|--|

| High Yield             | Planarized layer – protects features, DIW soluble                |  |

|                        | Continued support – film frame                                   |  |

|                        | Passive de-bond – no mechanical slide, peel, pull, or burning    |  |

| Adhesive               | Chemical & thermal resistant, soluble in tape-safe chemistry     |  |

| Simple & low-cost tool | De-bonding conducted within common wet-bench                     |  |

| High Throughput        | 100wph baseline                                                  |  |

| Taped film frame       | Compatible with tape-safe de-bond chemistry, DIW cleans          |  |

| Porous carrier recycle | No cleans required, 10 cycles before re-apply                    |  |

| Scalable               | Penetration/saturation is non-linear relative to substrate size; |  |

|                        | de-bond time increases by a minor factor                         |  |

| Green process          | Tape-safe de-bond, DIW cleans                                    |  |

#### Porous Coat & Insert

**Recycle Carriers**

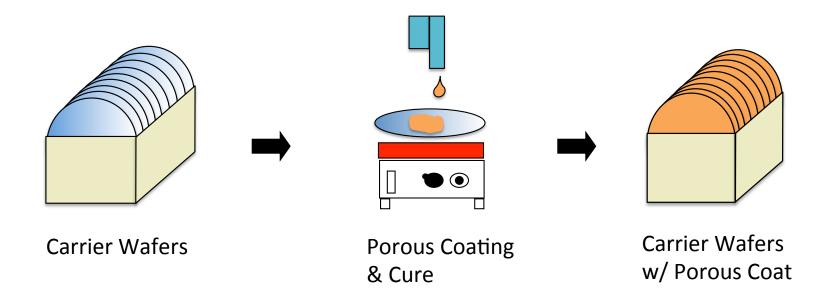

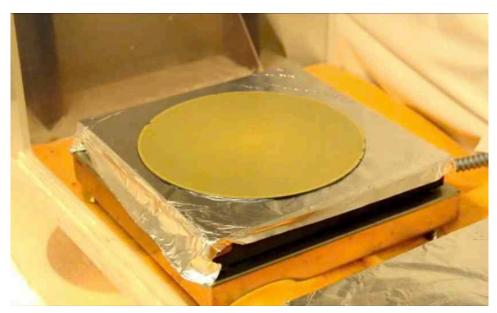

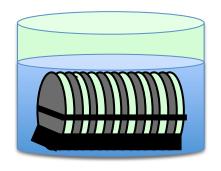

# Porous Coating on Carrier Wafers

## Formation of Porous Carrier

**Apply Coating to Si Wafer**

Porosity production during cure

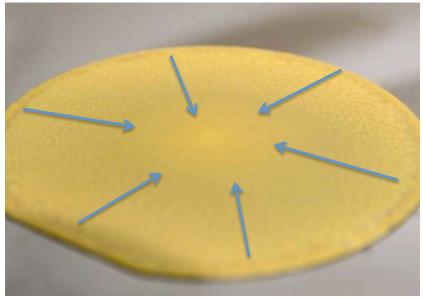

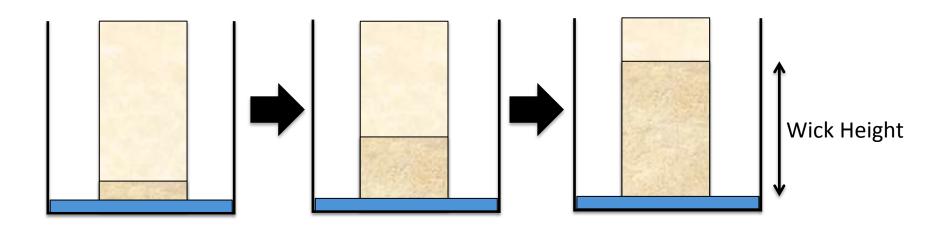

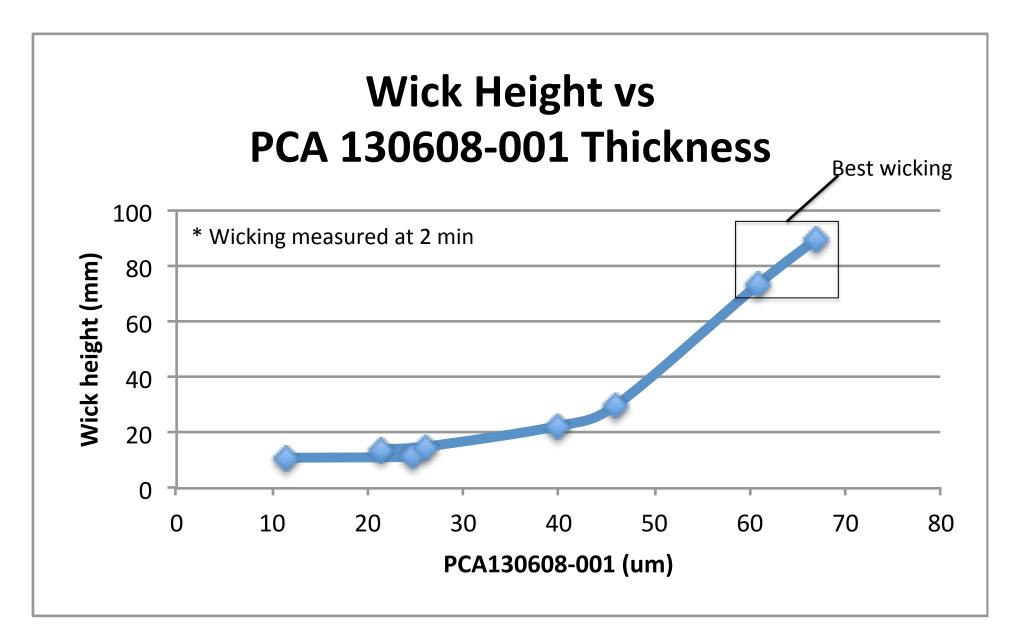

# Porosity Method (Wick)

- Daetec's method

- Application related to porosity

22

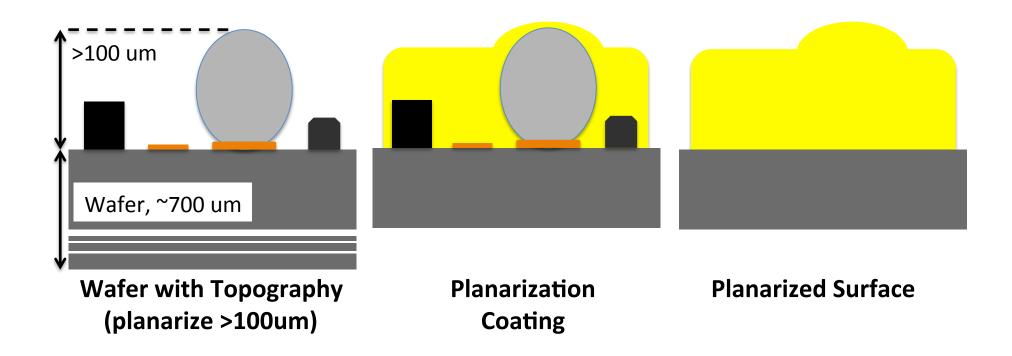

# **Planarization Coating**

- Planarizing over topography

- Achieves >100um thick coatings

- Rigid to protect during grind & handling

- Inert, non-crosslinking, no reaction with metals, organic materials

- Thermal resistance >300C

- DIW soluble, removed in tank #2

# **Planarization Coating**

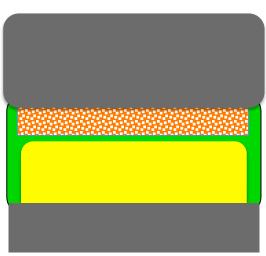

# Porous Carrier & Sealed System

Bonded & Sealed System

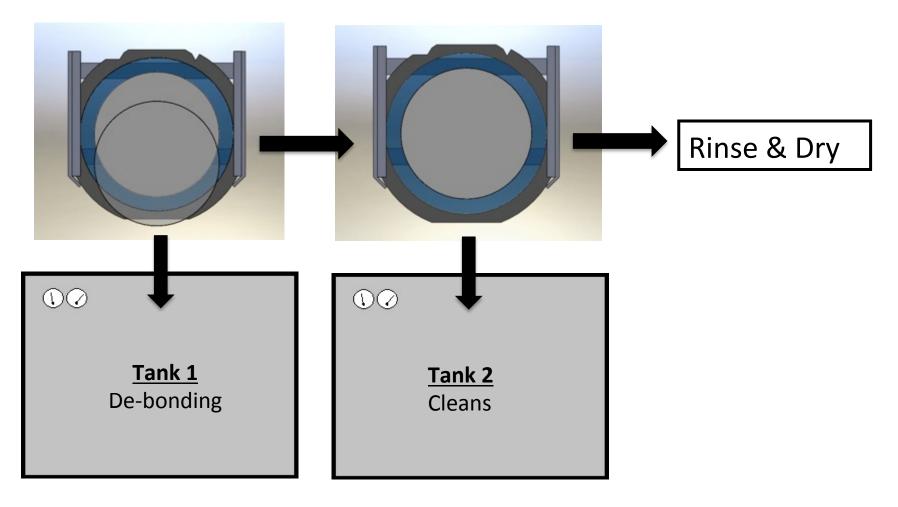

# De-Bonding & Cleans

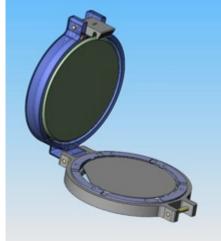

# Affix to Film Frame for Debond

Film frame attach Bonded stack

Daetec single wafer fixture

# **Debond Process**

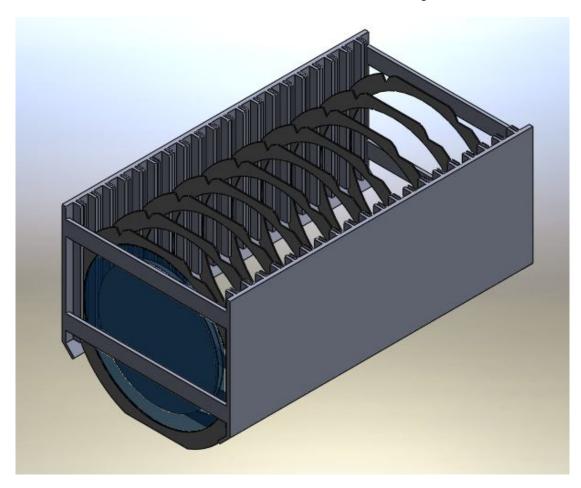

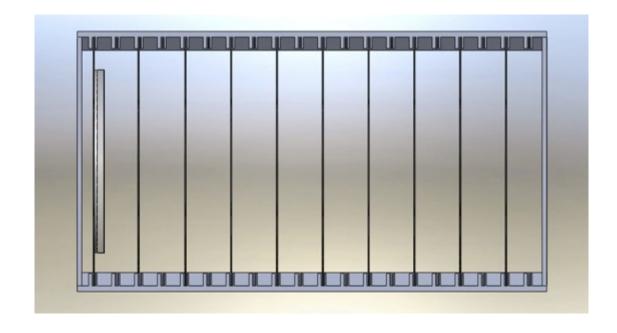

# Debond Fixture for Multiple Wafers

- Open-body design to allow chemistry circulation

- •Bonded film frame rings are vertically loaded into slots

#### Fixture Features

•Full scale processing: 20-25 wafers, <15 min

-OR

80 – 100 wafers,1 hr

• Prototype processing: 4 wafers, <15min

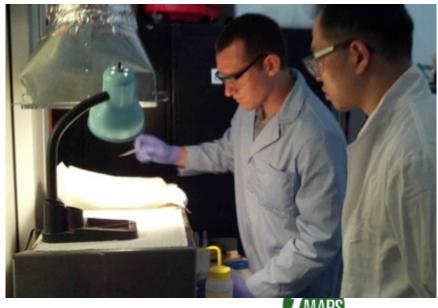

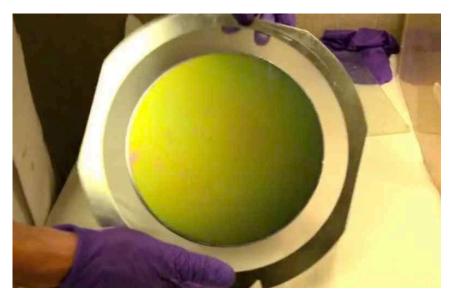

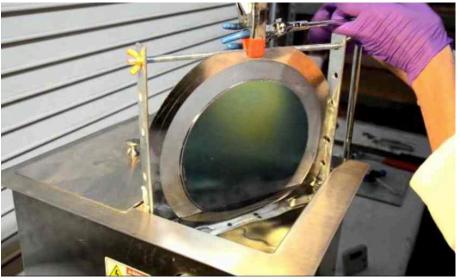

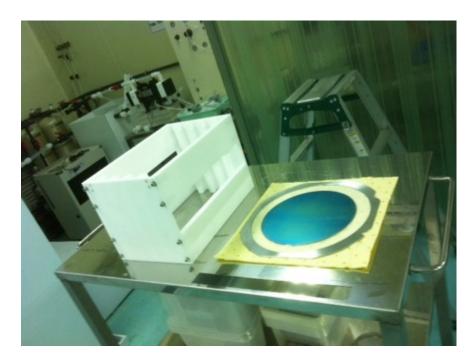

# Demo in Daetec's Tool

#### Wafer capability:

- 6"

- 8"

- 12"

#### **Tool Demonstration**

Fixture w/film frame

Operation in wet bench tool

# Process – Debond/Cleans

Slide/Debond + Clean

Max 20 wph

SW

Debond &

Cleans

Batch Demount & Cleans

Min 100 wph

Batch

Debond &

Cleans

(Wet Bench)

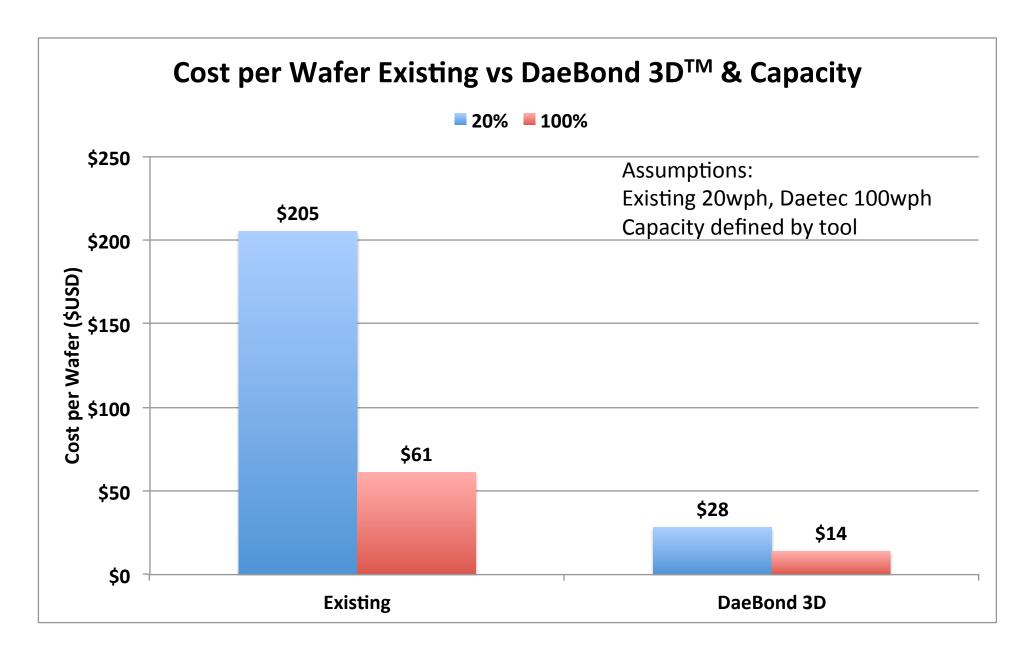

# Cost Comparision (for COO)

| Parameter                                   | Existing                    | DaeBond 3D™                   |

|---------------------------------------------|-----------------------------|-------------------------------|

| Adhesive                                    | Thermoplastic - rubber      | Thermoset - blend             |

| Carrier                                     | Silicon                     | Porous coat on silicon        |

| Materials                                   | Adhes. + solvent cleans     | Adhes. + porous coat + cleans |

| Materials cost per wafer (\$USD, <1m/>>10m) | \$25                        | \$25/\$10                     |

| Coating Application                         | Spin                        | Spin                          |

| Thermal Resistance (C)                      | 200-250                     | >250                          |

| De-bond Method                              | Thermal slide, peel         | Porous saturation             |

| De-bond tool type                           | Single Wafer; slide or peel | Batch; wet bench              |

| Tool cost (\$USD m)                         | 1.5                         | 0.75                          |

| Throughput (wph, per tool)                  | 20 (target)                 | 100 (minimum)                 |

| Cleans Chemistry                            | Solvent                     | Aqueous (5% in DIW)           |

# Materials Cost Projection

- Materials include cost on porous carrier and device wafer adhesive

- Estimates based upon 2 volume levels:

<1m wpy: ~\$25/wafer (\$28 w/tool)

>1m wpy: ~\$10/wafer (\$14 w/tool)

36

# COO by SEMI E35

- Ratio of technologies

- Cancel out several variables

| #   | Definition            | COO <sub>2</sub> vs. COO <sub>1</sub>                                       | Explanation                                  |

|-----|-----------------------|-----------------------------------------------------------------------------|----------------------------------------------|

| F\$ | Fixed Costs           | $F\$_1 = \$1.5m = 5 X R\$_1 (yr1)$<br>$F\$_2 = \$0.75m = 2.5 X R\$_2 (yr1)$ | Tool represented as materials cost           |

| R\$ | Recurring Costs       | $R\$_2 = R\$_1 = \$300K/yr$                                                 | Materials costs same;<br>12,000 wpy @ \$25/w |

| Y\$ | Yield Cost (scrap)    | Y\$ <sub>2</sub> = Y\$ <sub>1</sub> = 0                                     | Assume no loss                               |

| L   | <b>Equipment Life</b> | L <sub>2</sub> = L <sub>1</sub>                                             | Same life                                    |

| Т   | Throughput            | T <sub>2</sub> = 5 X T <sub>1</sub>                                         | batch vs SW = 5 X T <sub>1</sub>             |

| Υ   | Composite Yield       | $Y_2 = Y_1$                                                                 | Same yield                                   |

| U   | Utilization           | U <sub>2</sub> = U <sub>1</sub>                                             | Same maintenance                             |

$$COO = \frac{F\$ + R\$ + Y\$}{L \times T \times Y \times U}$$

$$\frac{COO_2}{COO_1} = \frac{DaeBond 3D}{Existing Technology}$$

$$\frac{COO_2}{COO_1} = \frac{F\$_2 \times T_1}{F\$_1 \times T_2} = \frac{F\$_2}{F\$_1 \times 5}$$

$$\frac{COO_2}{COO_1} = 10\%$$

# COO<sub>2</sub>/COO<sub>1</sub> Comparison Results

| Comparison of COO Technologies     | Tool costs<br>1) \$1.5m<br>2) \$0.75m | Tool costs<br>1) \$3m<br>2) \$0.5m |

|------------------------------------|---------------------------------------|------------------------------------|

| COO <sub>2</sub> /COO <sub>1</sub> | ~10%                                  | ~3%                                |

# 4. Summary

- DaeBond 3D is a disruptive tech for 3DIC

- Technology based upon a porous coating

- Porosity allows passive wafer de-bonding

- De-bonding occurs on film-frame tape

- Process finishes in a film-frame cassette

- Throughput is defined by cassette size and flow, minimum 100wph

#### Contact for More Information

- DAETEC provides development, consulting, and technical training/support to solve manufacturing problems and introduce new options of doing business.

- Diversified Applications Engineering Technologies (DAETEC)

Camarillo, CA (USA) (805) 484-5546

imoore@daetec.com; www.DAETEC.com