# Temporary Bonding of Wafers, Displays, and Components

Jared Pettit, Alex Brewer, Alman Law, and John Moore Daetec, LLC

IMAPS Device Packaging Conference March 2015

#### **Contents**

- 1. Adhesives & Substrates

- 2. Wafers

- 3. Displays

- 4. Devices

### **Electronics Everywhere**

- Auto & Medical diagnostics

- Aircraft entertainment

- Communication

- IOT surveillance & traffic

2015 Arizona IMAPS Device Pkg Conference

#### **Thin Substrate Market Drivers**

- Electronics trending thinner

- Smart phones, tablets, etc.

- Diced chips are stacked

- Stacked chips used in all functional devices

- Extremely fragile

- Requires a temporary support

#### 1. Adhesives & Substrates

- Matched to substrate needs

- Surface energy (lower vs substrate)

- Thermal & chemical resistant

- Low outgas (high Tg or barrier)

- Inert & easy to clean

# World of Temporary Bonding

| Work<br>Unit           | Market                        | <b>DaeCoat</b> <sup>TM</sup> | Method                                                              |  |

|------------------------|-------------------------------|------------------------------|---------------------------------------------------------------------|--|

| Organic<br>Film        | OLED,                         | 350                          | Cure on carrier, bond w/pressure                                    |  |

| Organic<br>Film (cast) | flexible<br>displays          | 310                          | Cure on carrier, cast & cure liquid                                 |  |

| Thin glass             | TFT<br>LCD                    | 350                          | Cure on carrier, bond w/pressure                                    |  |

| Foil                   | OLED,<br>flexible<br>displays | 350                          | Cure on carrier, bond w/pressure                                    |  |

| Wafer                  | 3DIC                          | 350, 615,<br>620             | Planarize<br>wafer w/550,<br>cure on<br>carrier, bond<br>w/pressure |  |

| Die (chip)             |                               | 350                          | Cure on carrier, bond w/pressure                                    |  |

# Substrate Types

- Rigid: silicon, quartz, glass, sapphire

- Flexible: PI, PEN, Arylite, PPS, PET, epoxy

- Ideal characteristics: CTE match, low TTV

- Other qualities: transparency, tensile, barrier

- Dimensions: application specific

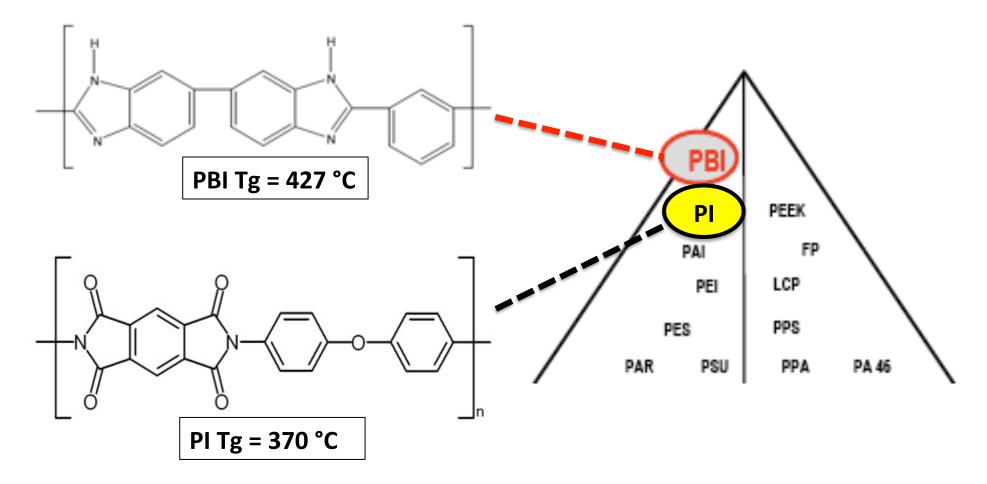

# **Engineering Polymers**

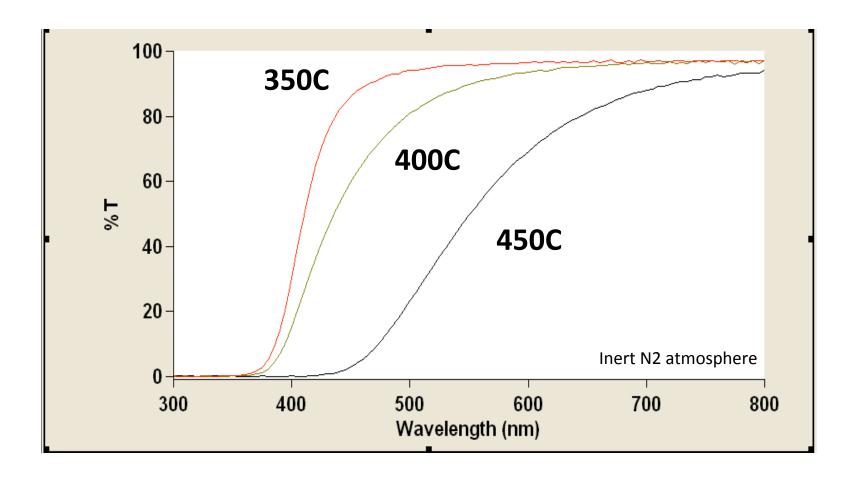

# Typical PI Transparency Thermal Trend

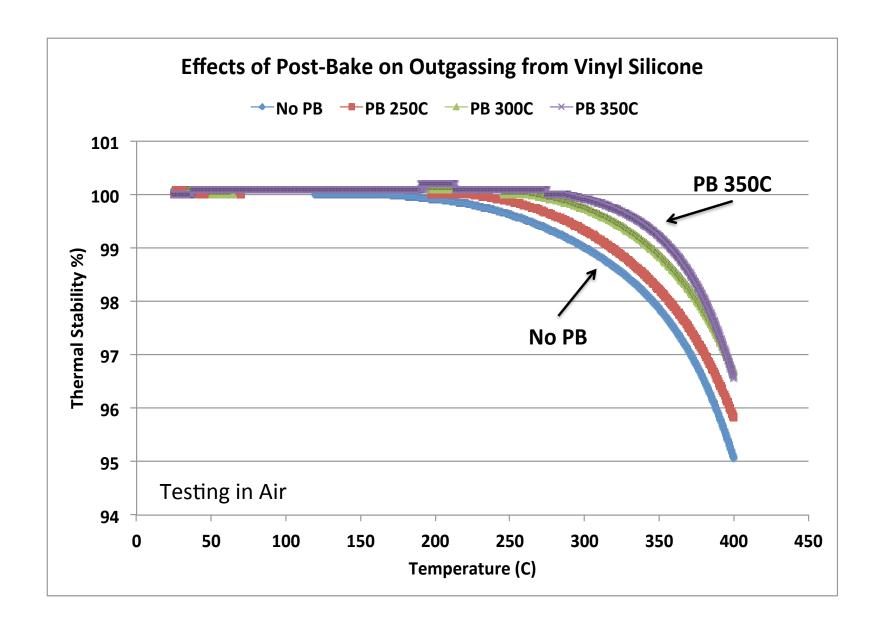

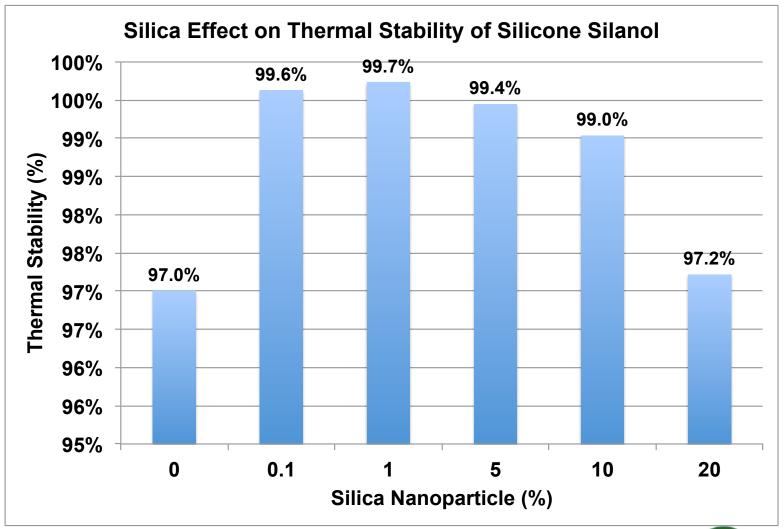

# Silicone Thermoset (catalytic)

Resin monomer (MW & shape)

Free-Radical

**Activator monomer (MW & shape)**

**Silicone Polymer**

#### Silicone 400C Thermal Resistance

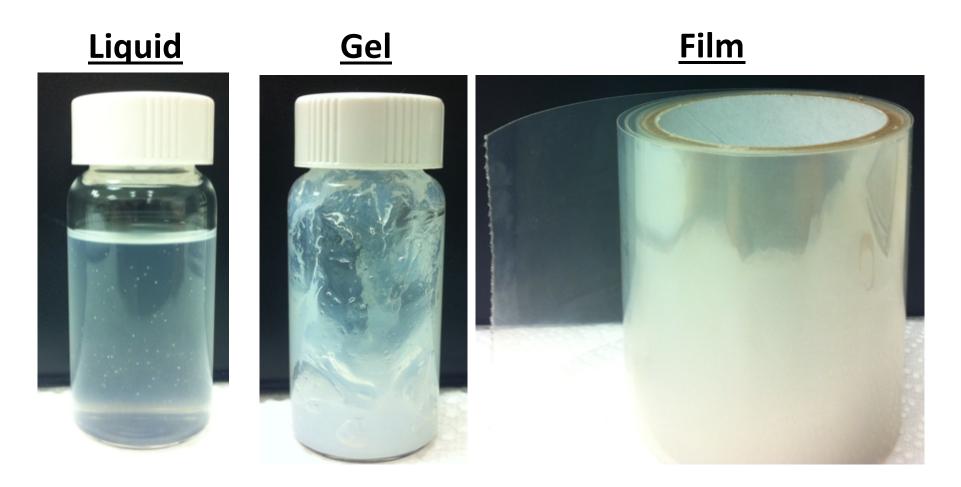

# Adhesive in Several Forms

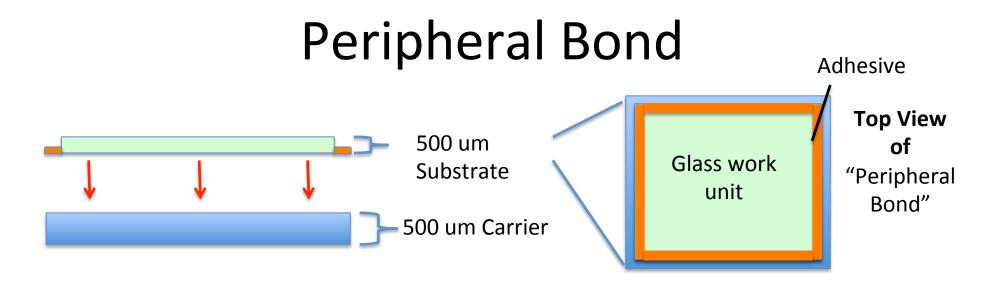

- The adhesive may be applied on the edges of the carrier – known as peripheral bond

- Thin substrate is bonded onto carrier

- Adhesive undergoes heat cure

**☼** 7.periph. bond

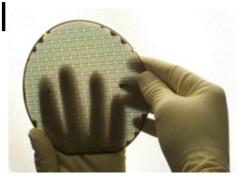

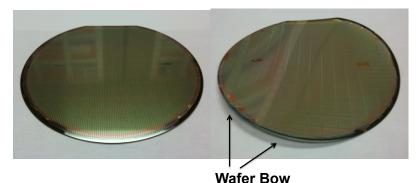

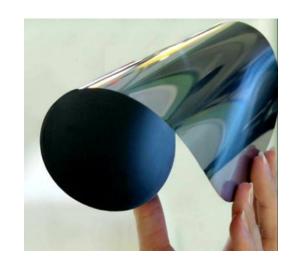

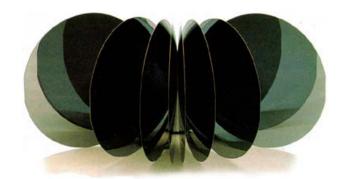

#### 2. Wafers

- Wafers thinned to <100um</li>

- Carriers are required

- Debonding generates problems, can be a bottleneck, high cost, and source of yield loss

# Creating a Process

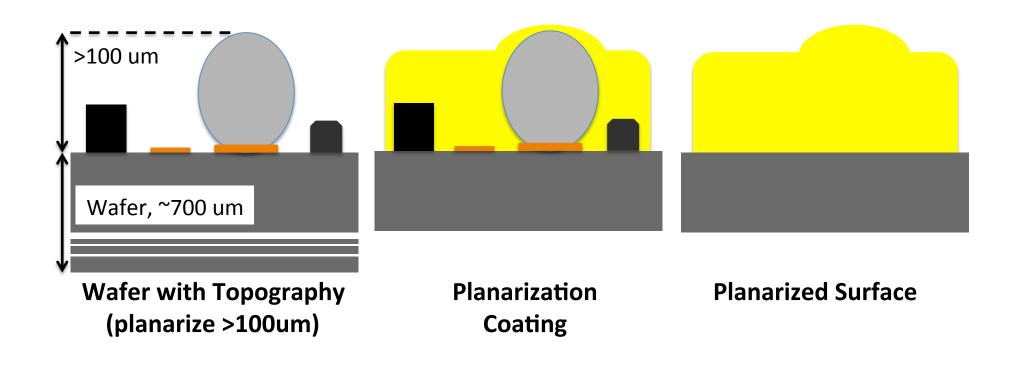

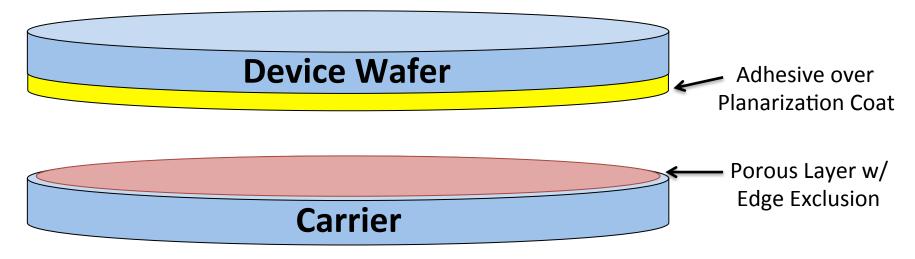

- Device Wafer: planarized, edge trim (thickness)

- Carrier: CTE closely matched, TTV <2um</li>

- Adhesive: thermal & chemical resistant, thin & uniform, if thick (high modulus)

- Bond: low temp (CTE)

- Debond: passive & cleans complete

# **Planarization Coating**

DaeCoat<sup>™</sup> 515 – DIW washable

# **Carriers**

- Silicon

- Glass

- Sapphire

- Tape

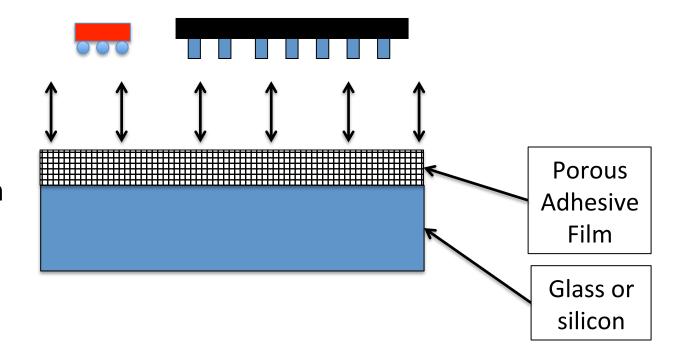

#### **Porous Carriers**

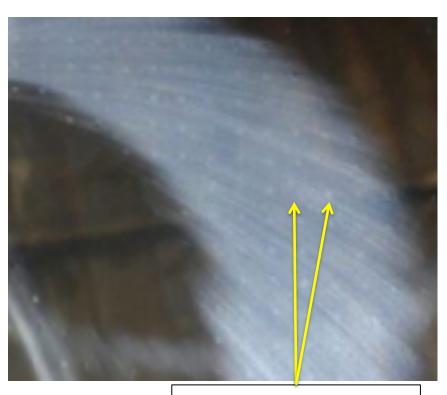

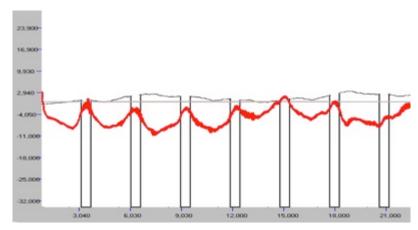

# Perforated Glass, 50 μm

Black: Surface Scan of Perforated carrier Red: Surface Scan of ground wafer with perforated carrier

Divots from glass pores

Surface Scan shows the divots from glass pores

#### **Porous Carrier**

#### **Benefits**

- Thermal & chemical resistant

- Simple bond, high adhesion

- Accepts many adhesive types

- Passive debond (chemical diffusion)

- Device wafer on film frame

- Recycle >10X

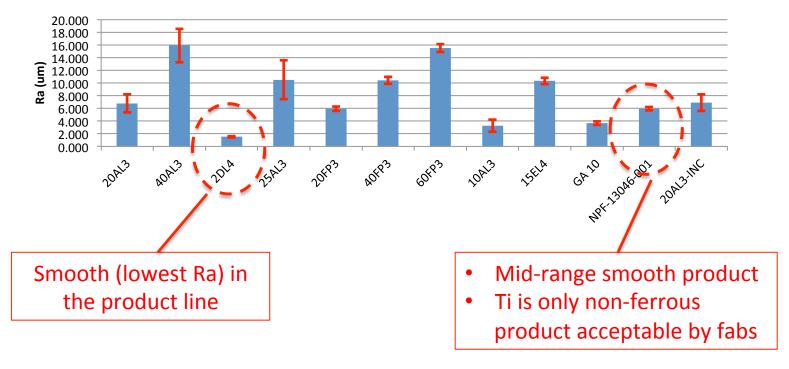

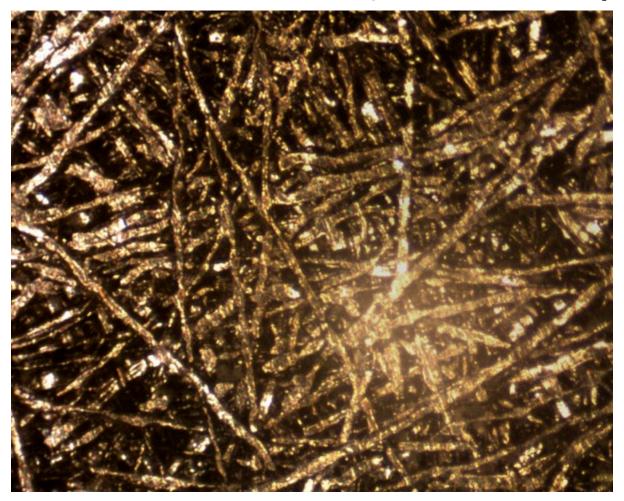

#### Porous Metal Carrier Media

# Ti Porous Metal (Microscopic)

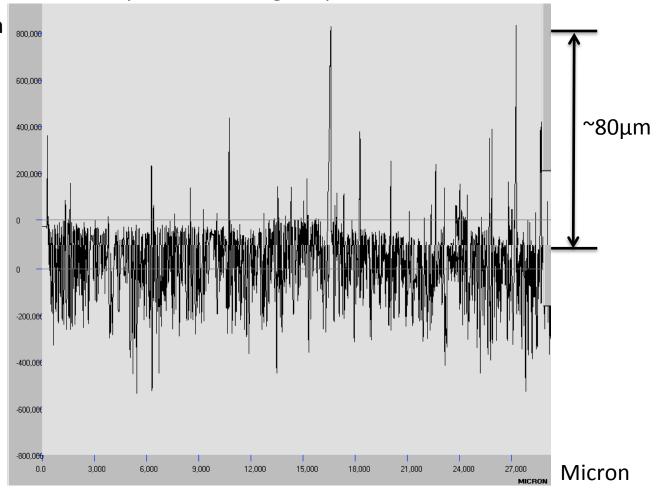

#### Surface Scan of Porous Ti

Ti has stray wires reaching <80μm

Angstrom

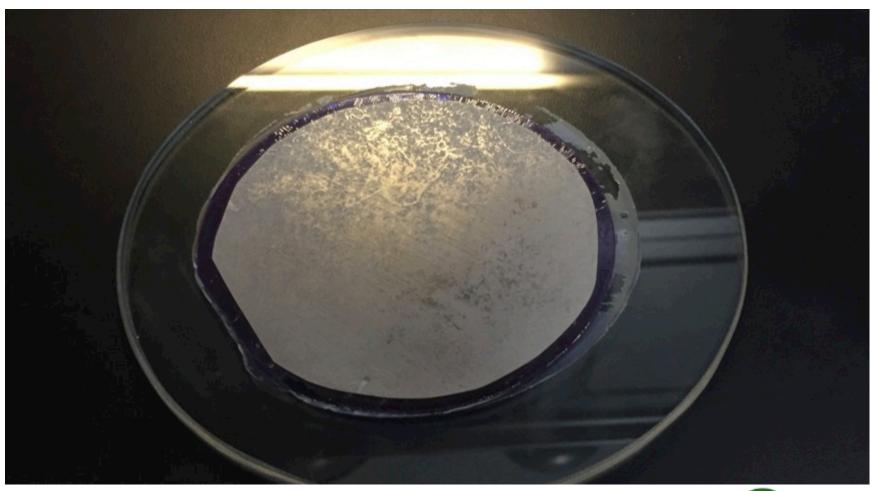

# Porous Metal Carrier Polishing to TTV

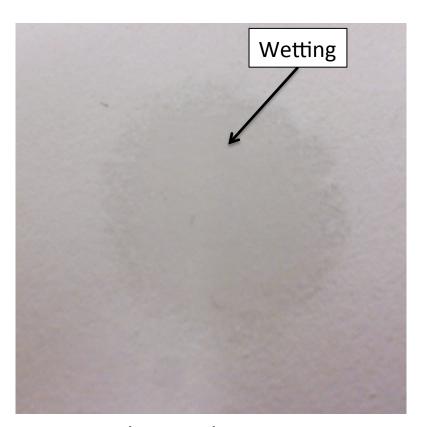

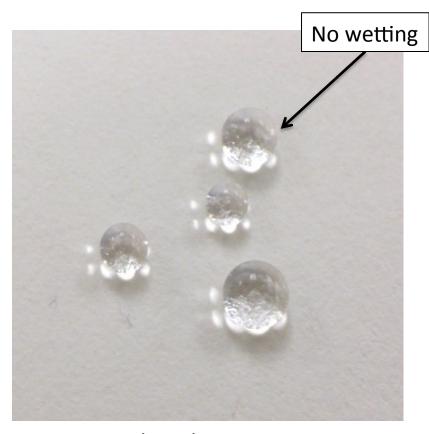

#### **Surface Treatment**

Without Exclusion Layer

With Exclusion Layer

# Wafer Grinding & Testing

Strausbaugh

- Use a local grind/polish firm (Arizona, USA)

- Equipment is consistent with that used in fabs

- Scientists have a high degree of experience

**Process**

# Commercial Technologies

|                       | BSI<br>(Zonebond)         | 3M                        | TMAT                      | Dupont                                       | Dow Corning                  | DOW                                   |

|-----------------------|---------------------------|---------------------------|---------------------------|----------------------------------------------|------------------------------|---------------------------------------|

| Bond type             | Thermoplastic             | Thermoset                 | Thermoset                 | Thermoplastic                                | Thermoset                    | Thermoplastic                         |

| Debond type           | Slide + CRT<br>/Peel      | Laser, Peel               | Peel                      | Laser + CRT                                  | Peel                         | Peel                                  |

| Tooling               | Thermoslide/Peel<br>tool  | Laser tool,<br>Peel tool  | Peel tool                 | Laser tool,<br>Peel tool                     | Peel tool                    | Peel tool                             |

| Post processing       | Cleans,<br>tape isolation | Cleans,<br>Tape isolation | Cleans,<br>Tape isolation | Cleans,<br>Tape isolation                    | Cleans,<br>tape<br>isolation | Cleans,<br>tape isolation             |

| Temperature           | ≤250°C                    | ≤250°C                    | ≤300°C                    | ≤450°C                                       | ≤300°C                       | >300°C                                |

| Additional challenges | Cleans                    | Transparent carriers      | None                      | Transparent carriers<br>Lengthy curing cycle | Cleans                       | None                                  |

| Key benefits          | RT Debond                 | RT Debond                 | RT Debond                 | High temp<br>processing, RT<br>debond        | RT Debond                    | High temp<br>processing, RT<br>debond |

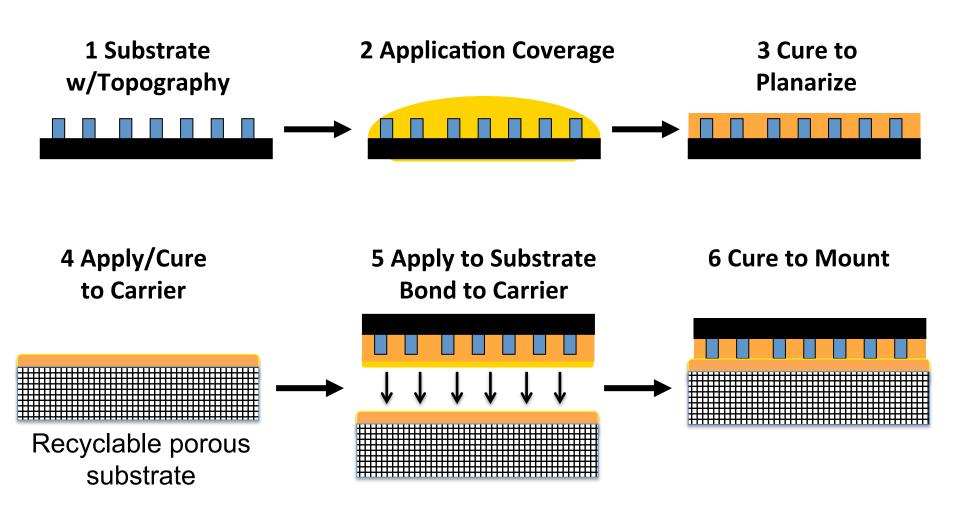

#### Process Flow – Porous Carrier

# Silicon Substrate Subsequent Steps Thin Debond Apply Adhesive Apply Adhesive to silicon device Subsequent Steps Thin Debond Dry-Bond 25-30C, 5min in Bonder (Pressure ~15psi)

# 3. Displays

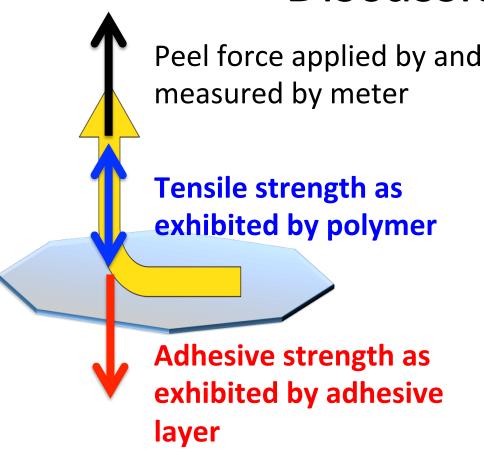

#### Discussion

Model of thin substrate peeling with adhesive layer, minimizing bubble formation

#### **Bubble Model**

Bubble forms when force of irregularity > adhesive

Force exhibited by gas or other irregularities

Adhesive strength as exhibited by adhesive layer

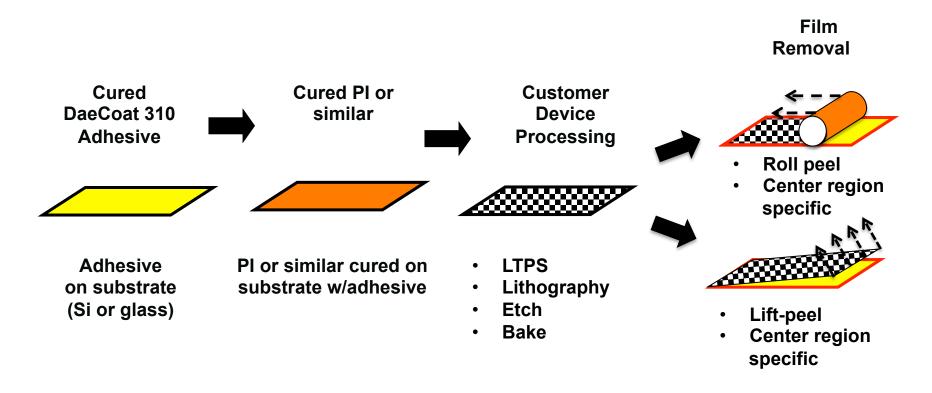

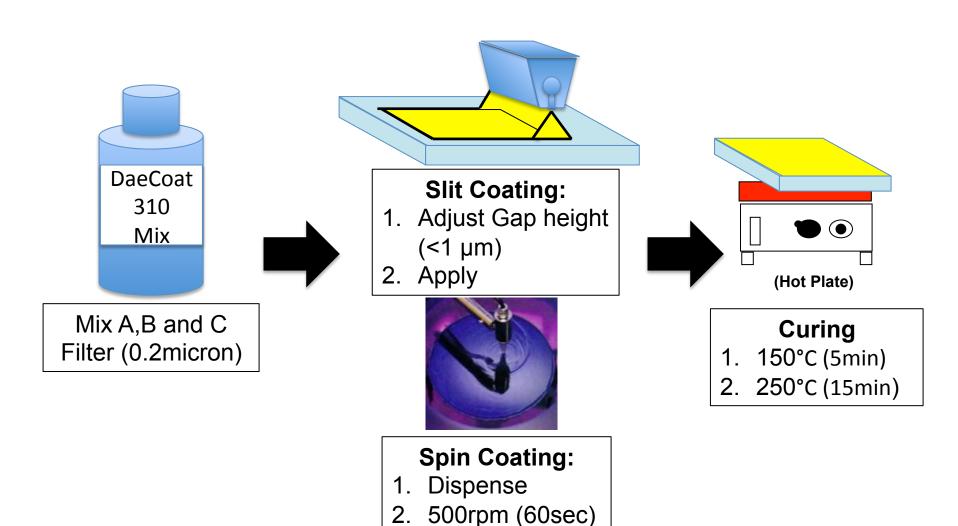

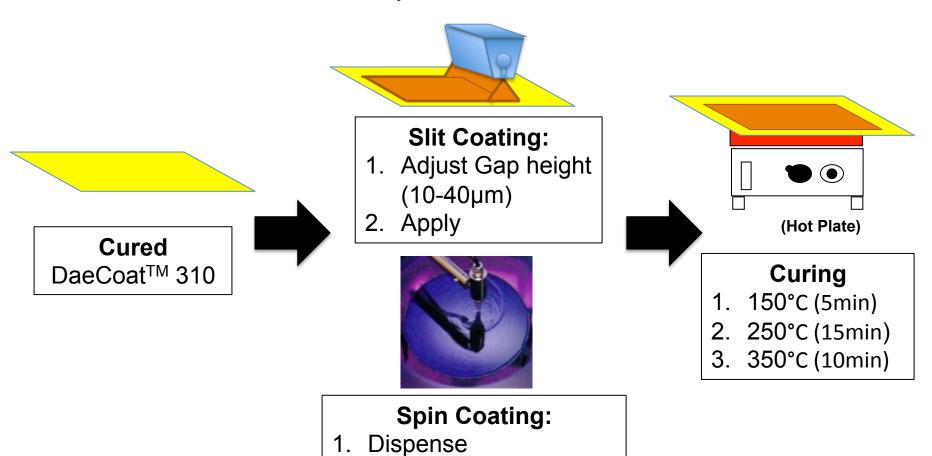

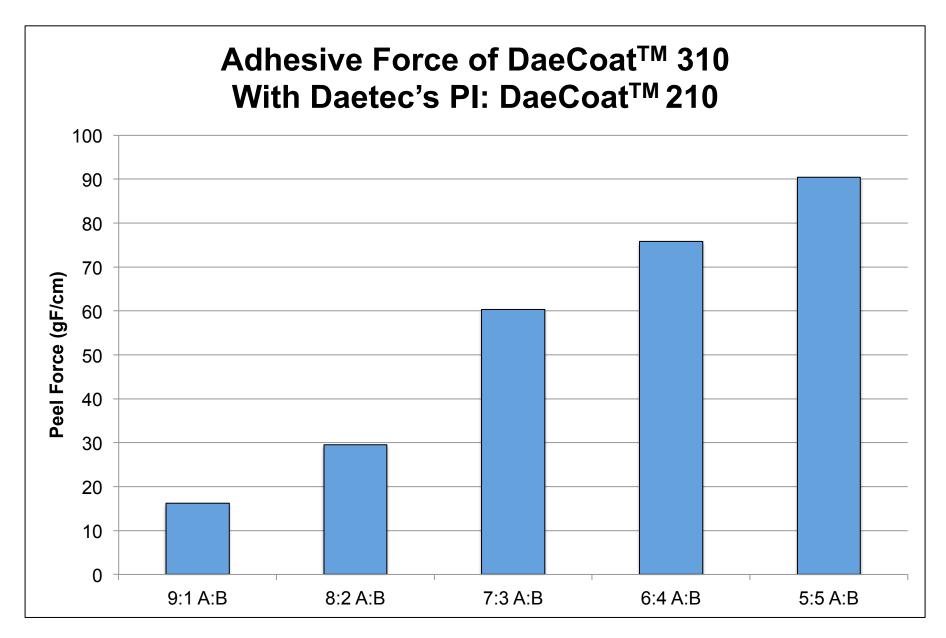

# Adhesive: DaeCoat™ 310

# PI or Similar Coating

Daetec's Polyimide: DaeCoat™ 210

2015 Arizona IMAPS Device Pkg Conference

1000-2000rpm (60sec)

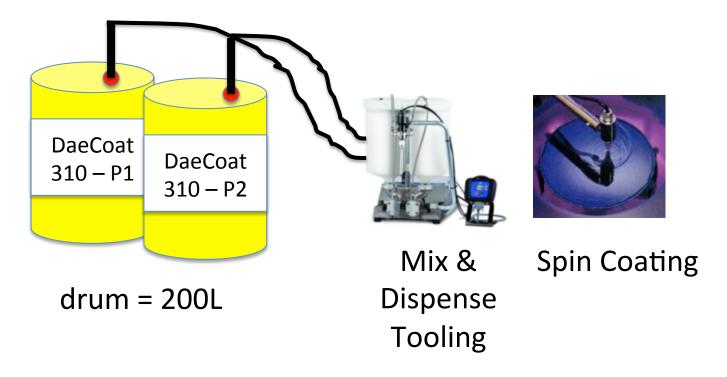

# High Volume Manufacturing

DaeCoat<sup>TM</sup> 310 components are stable for long shelf-life prior to mixing.

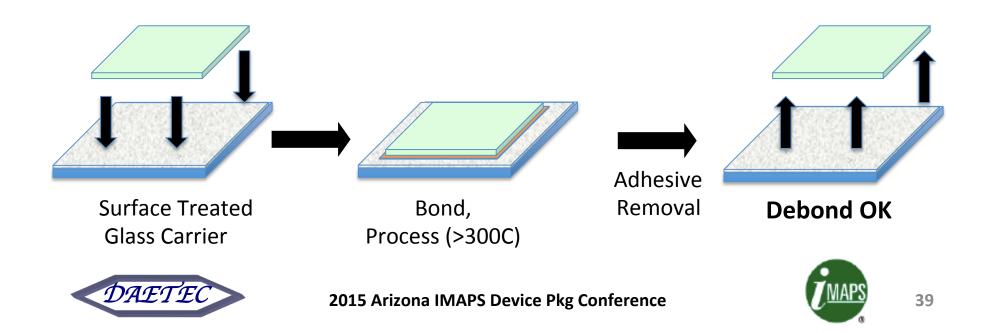

## Glass on Glass Bonding

- To prevent fusion, carrier is treated

- Allows glass substrate to debond after high temp processing

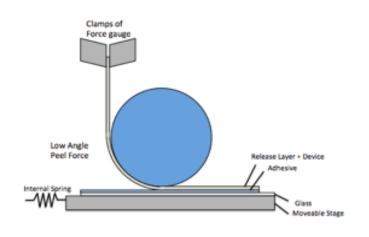

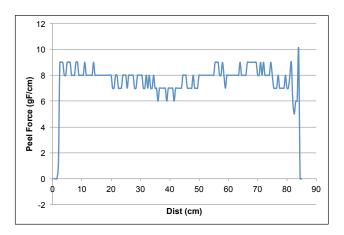

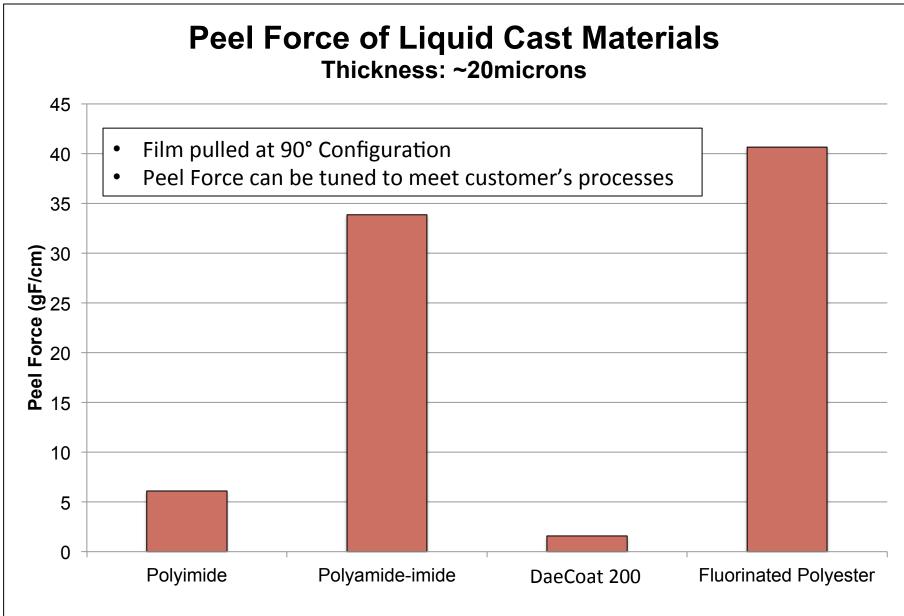

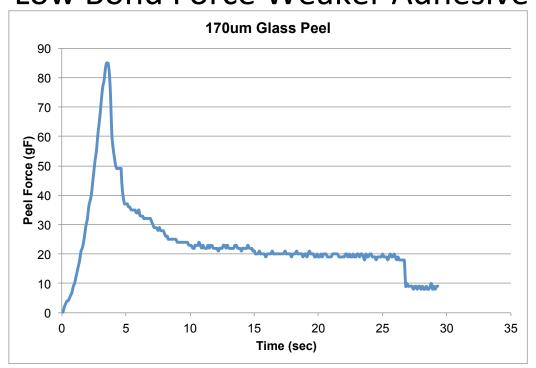

# Controlled Adhesion: Edge Pull

#### Low Bond Force Weaker Adhesive

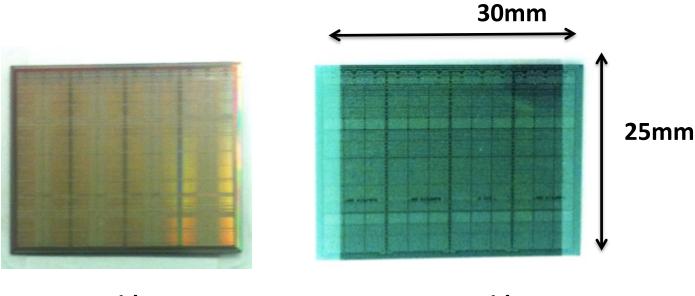

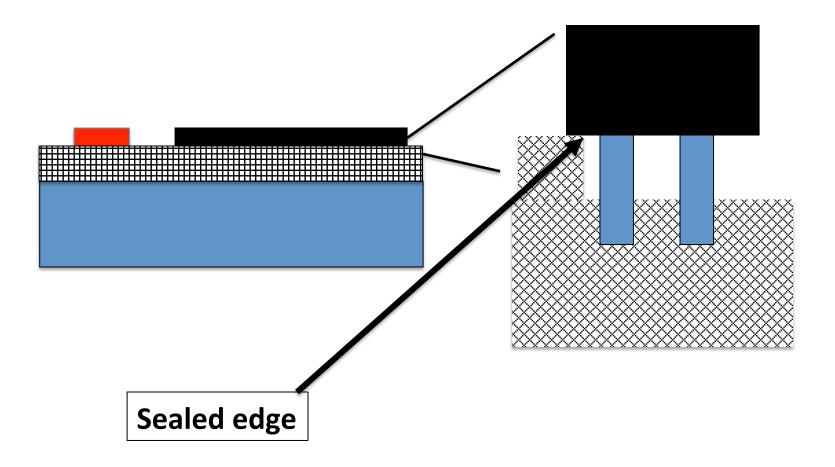

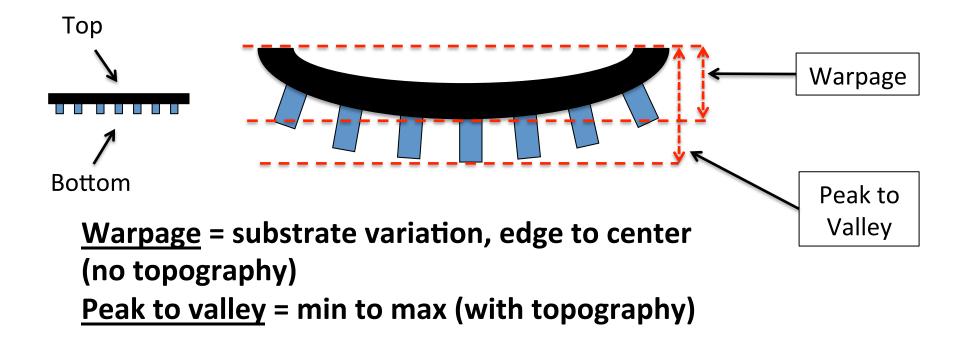

#### 4. Devices

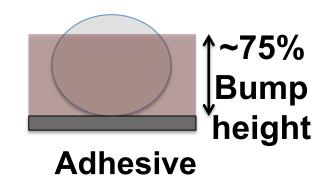

Thin Silicon Interposers (TSIs)

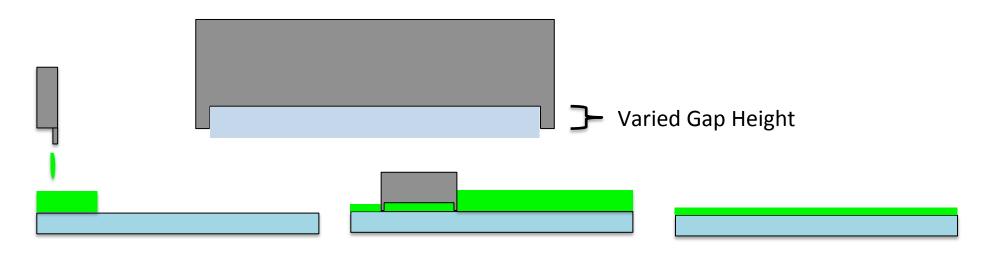

- Substrate ~100um thickness

- Underlying bumps ~100um height

Top side

Bottom side (contains solder bumps)

#### **Application**

#### Post-Bonding Process

#### Adhesive Planarization

#### Planarization and Thermal

#### **Porous Carrier**

Porosity higher for inside material (A). Outer coating (B) is lower porosity **Porous** A = 0.5 - 0.8mm Carrier B = 0.1 - 0.25mm C = 0.5 - 1 mmTSI on adhesive

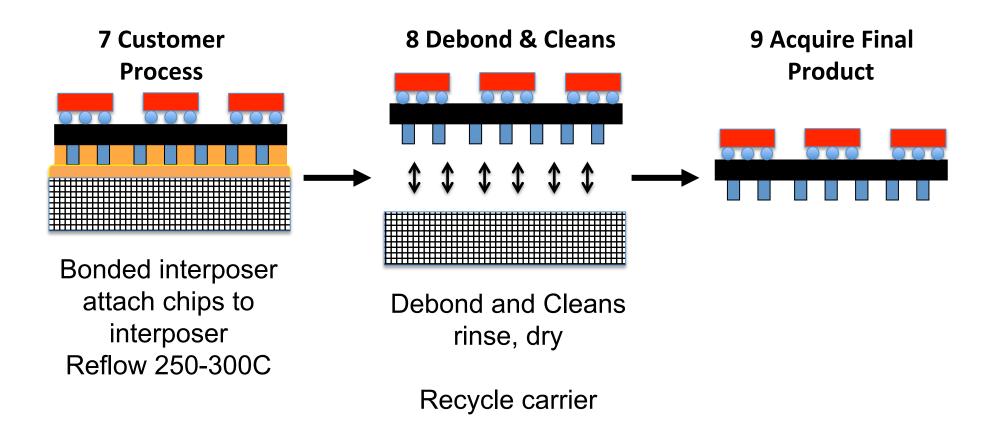

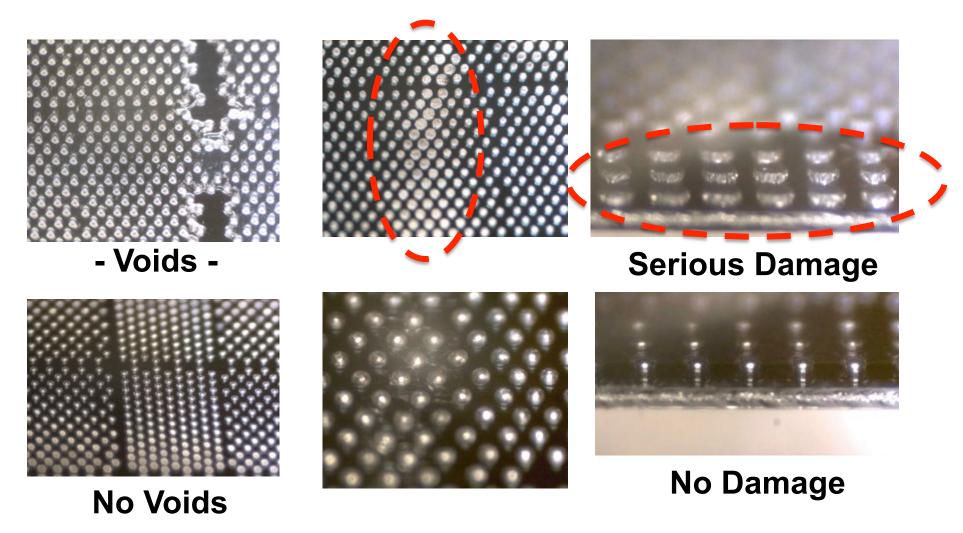

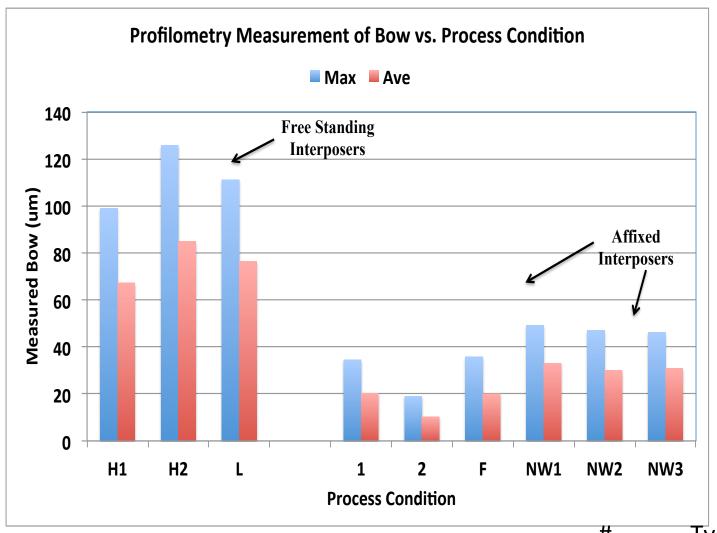

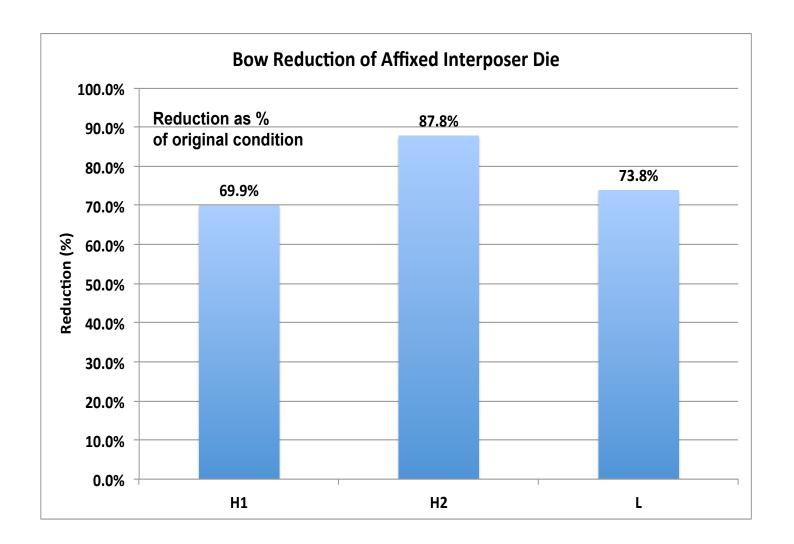

### Results - baseline TSI

#### Results - Bonded TSI

Variation <12um

# Type1, 2, F PeripheralNW Porous Subst

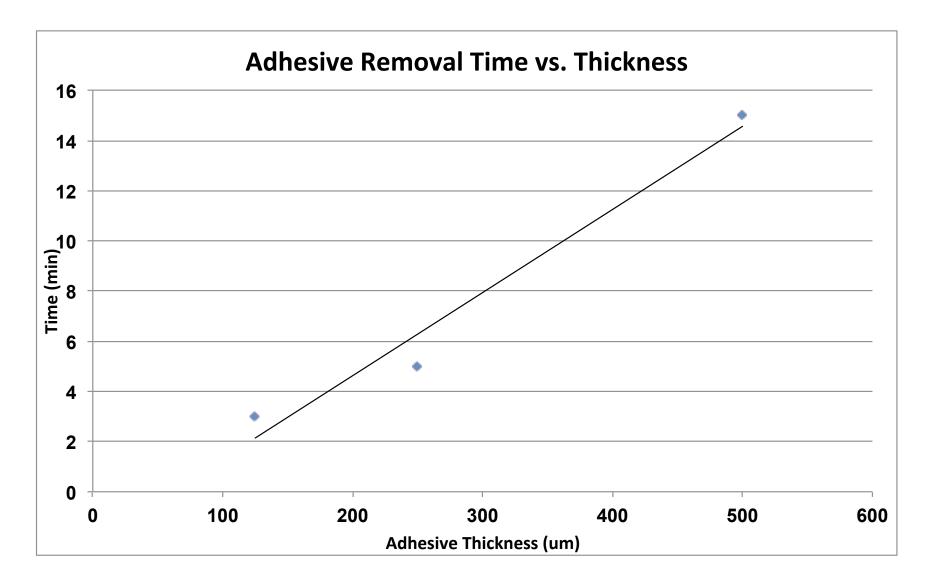

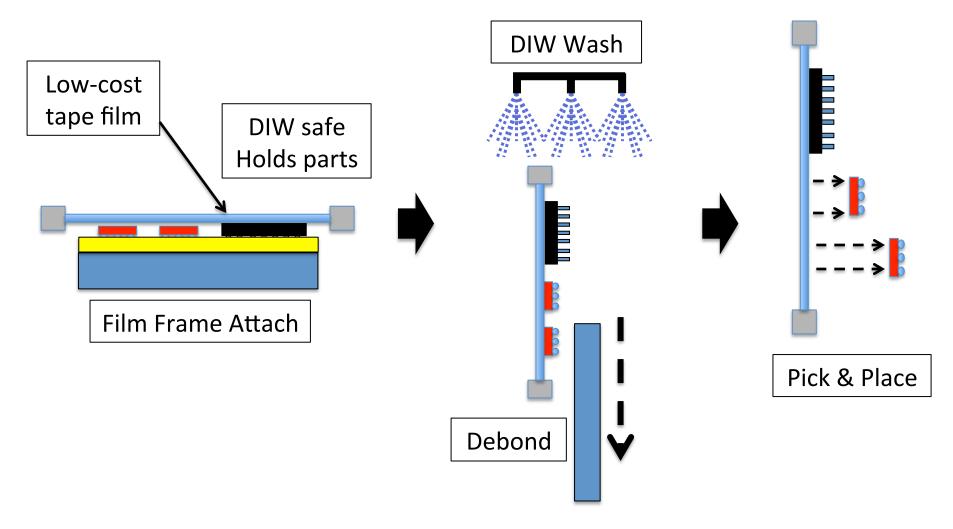

## Results – DeBonding

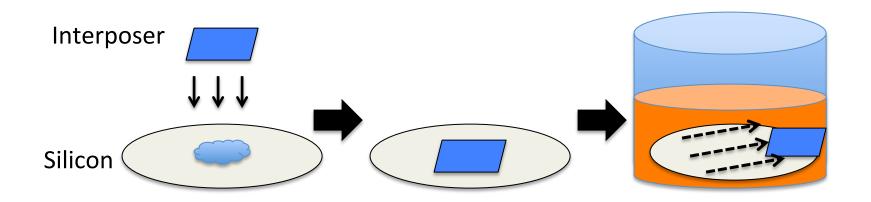

Prior activity involved applying adhesive to interposer & silicon wafer, holding interposer in place

Bond interposer to silicon wafer, observe flatness and other process details

Debond from silicon in Daetec digesting fluid, observe time

## Devices (cont.)

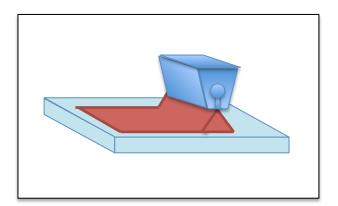

- Desire to attach device, process, remove with no residue. Adhesive is thermal & chemical resistant, conforms to device substrate

- Various adhesives are available

- Device substrates can be irregular

- Bond/edge seal (A) desired, best w/thickness

- Adhesive may be applied by several methods

- Carrier recycle with cleaning

- Total cost must be considered

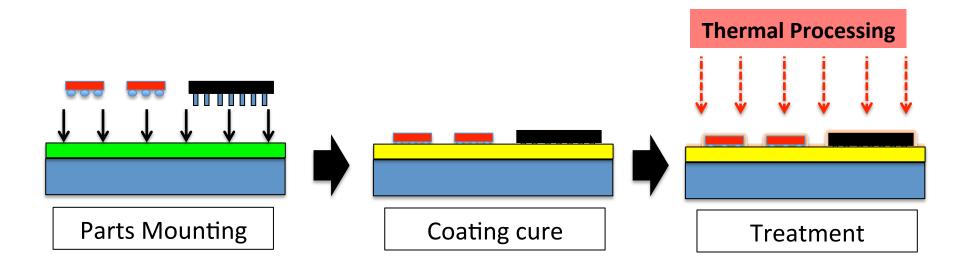

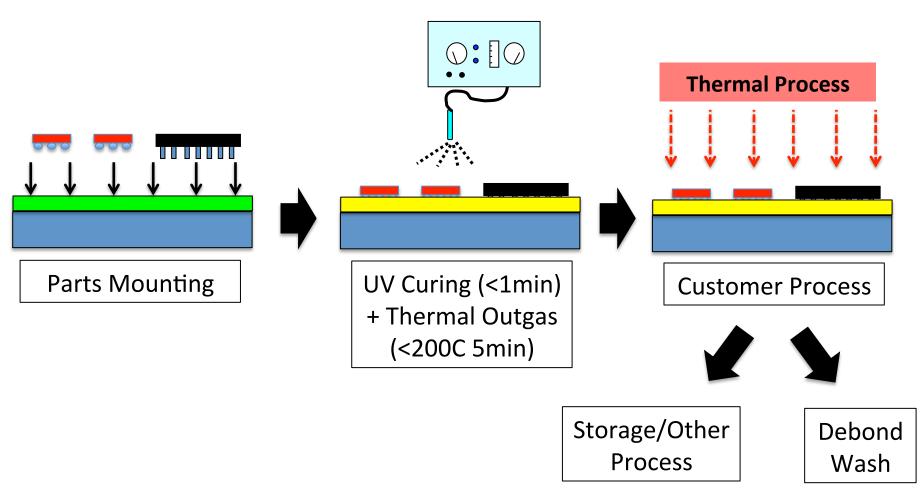

# **Component Bonding**

# **Small Devices for Thermal Processing**

#### **Appearance of Bottom**

| Name                   | #1              | #2              | #3              |

|------------------------|-----------------|-----------------|-----------------|

| Dimension              | 0.95cm x 0.95cm | 1.65cm x 1.15cm | 0.95cm x 0.95cm |

| Overview               |                 |                 |                 |

| Microscopic<br>Picture |                 |                 |                 |

## **Process Description**

#### **Process Description**

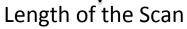

Adhesive is applied as a film to carrier on Thick Glass, Open-Faced

## Substrate Description

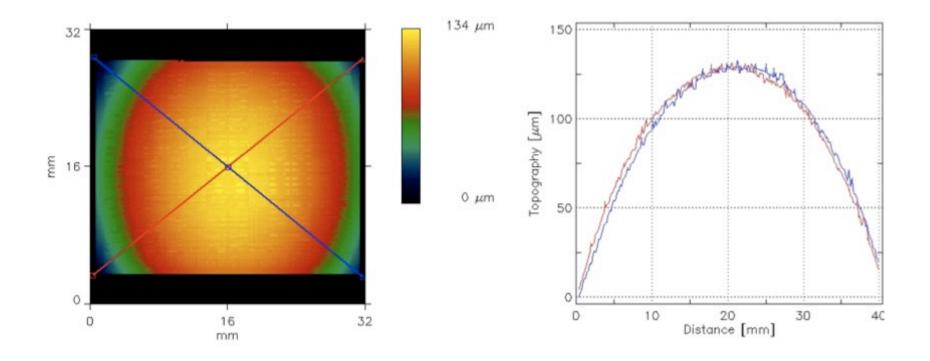

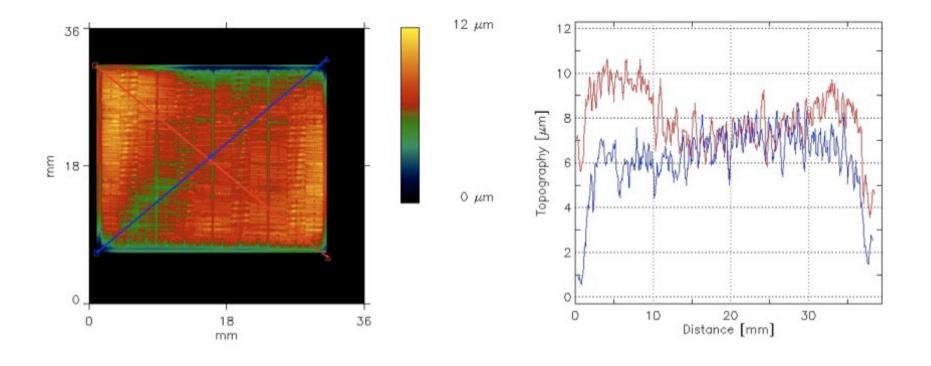

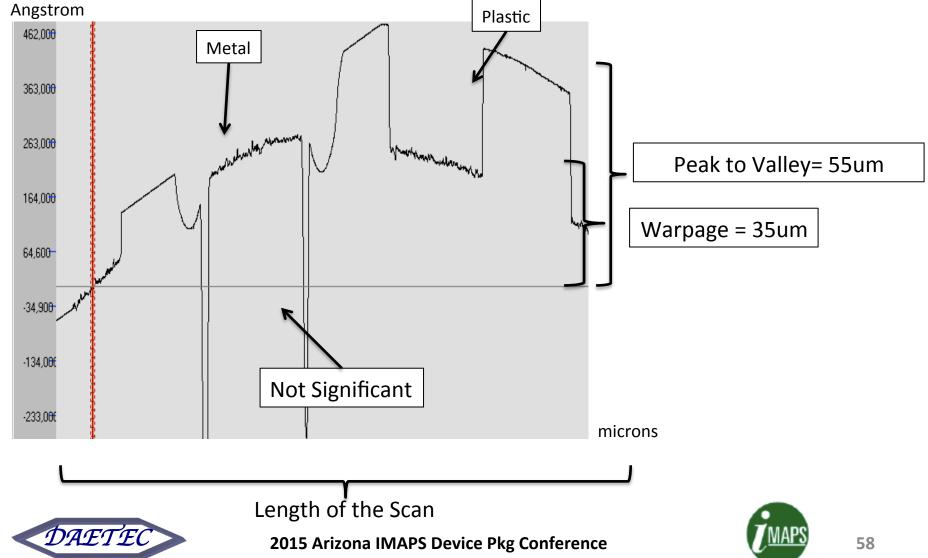

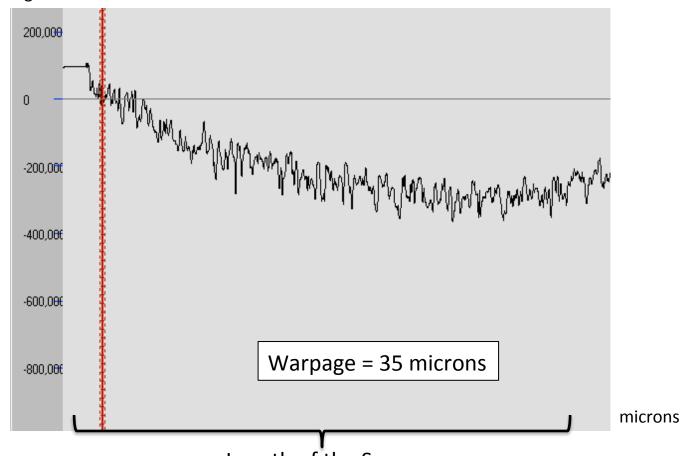

#### Surface Scan (Bottom of Substrate #1)

# Surface Scan (Top of Substrate #1)

## Ability to Bond & Seal w/Topography

Use of various DaeCoat products

| Substrate | Peak to<br>Valley<br>(μm) | Warpage<br>(μm) | Adhesive<br>thickness<br><60µm | Adhesive<br>thickness<br>>60µm |

|-----------|---------------------------|-----------------|--------------------------------|--------------------------------|

| #1        | 55                        | 35              | В                              | В                              |

| #2        | 14                        | <5              | Α                              | Α                              |

| #3        | 26                        | 23              | В                              | В                              |

A= Bond + Edge Seal (Ideal Process)

**B= Bond**

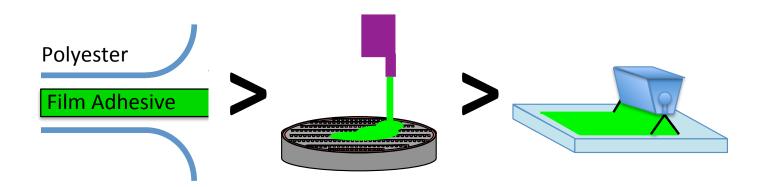

# Adhesive Film - Options

Use as B-stage film, thickness can vary

Slit-coating to substrates,

SB cure, process as

desired

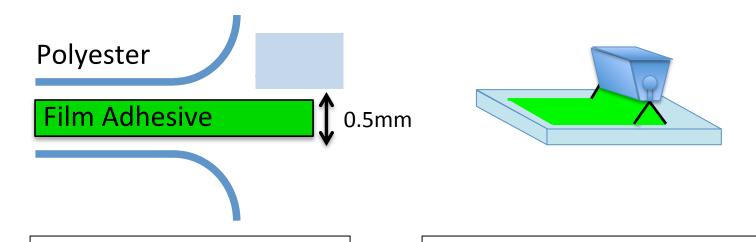

# Film w/Release Layers

- Aqueous-based adhesive

- Thickness = 20mil ~500um ~0.5mm

- No backing

- Sandwiched between PET release layers

- Remove 1<sup>st</sup> PET liner, apply to substrate

- Use a rubber roller, apply exposed adhesive to substrate, increase pressure onto PET facing up, remove 2<sup>nd</sup> PET liner, proceed with bonding

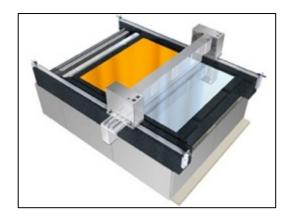

# Slit Coating

#### **Cost Considerations**

| Parameter          | Film w/release<br>liners | Spin Coating | Slit Coating |

|--------------------|--------------------------|--------------|--------------|

| Coating solids (%) | 80-100                   | <100         | 100          |

| Cost (\$/cm2)*     | <0.05                    | <0.05        | <0.02        |

| Convenience        | High                     | Med          | Med          |

| Tool Required      | -none-                   | coater       | coater       |

<sup>\*</sup>assume best case conditions with max solids for coating capability

# **UV Cure Film/Coating**

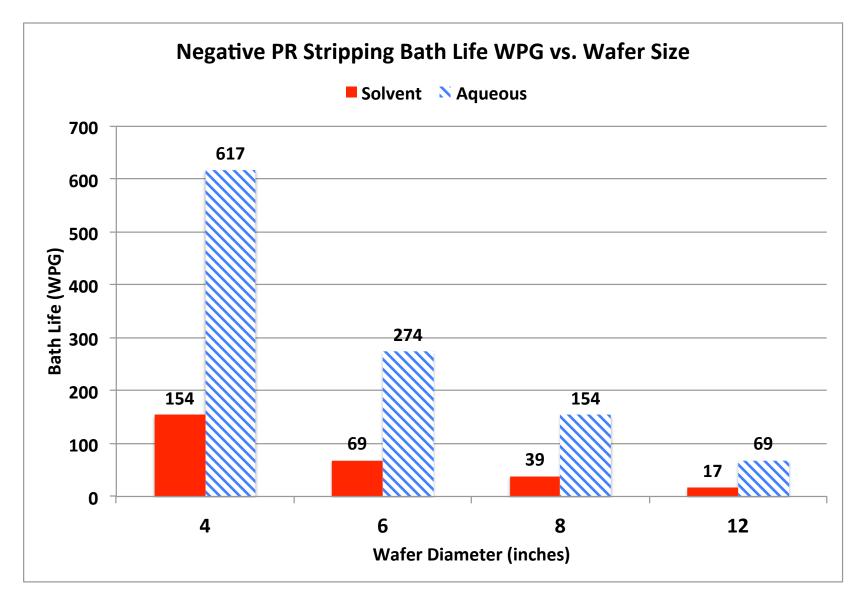

# Debond/Rinsing

#### Summary

- Temporary bonding technologies are being used for wafers, displays, and devices

- Key practices include variations around peel practices

- Cross-pollination continues to drive more creative development in different markets

- Improved yield, cost control, and simplicity are drivers

#### Contact for More Information

- DAETEC provides development, consulting, and technical training/support to solve manufacturing problems and introduce new options of doing business.

- Diversified Applications Engineering Technologies (DAETEC)

Camarillo, CA (USA) (805) 484-5546

imoore@daetec.com; www.DAETEC.com